## Organisatorisches

- Über mich: Josephine, 3. Semester Elektrotechnik

- Webseite: <a href="https://www.n.ethz.ch/student/jloehle/">https://www.n.ethz.ch/student/jloehle/</a>

- Folien, Zusammenfassung, Notizen

- Email: <u>iloehle@student.ethz.ch</u>

#### **Ablauf**

- 9:00-10:30: Theorie 1

- Kurze Pause

- 10:40-12:00: Theorie 2

- Mittagspause

- 13:00-16:00: Prüfung lösen + Zeit für Fragen

# Logische Verknüpfungen

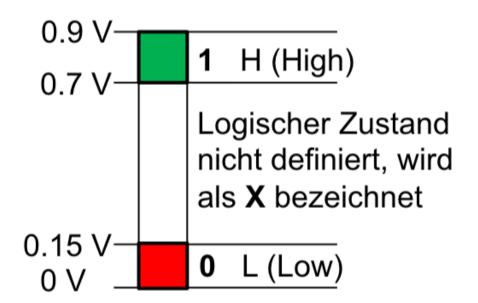

## Zweiwertige Logik – Bits

#### **Bits**

- 2 binäre Zustände: 0 & 1

- n Bits können 2<sup>n</sup> Zustände beschreiben

- MSB ... LSB

### Wahrheitstabellen

- N Eingänge

- M Ausgänge

| 2^N | Zei | len |

|-----|-----|-----|

|-----|-----|-----|

| Α | В | С | Υ                      |

|---|---|---|------------------------|

| 0 | 0 | 0 | $f(0,0,0) \in \{0,1\}$ |

| 0 | 0 | 1 | $f(0,0,1) \in \{0,1\}$ |

| 0 | 1 | 0 | $f(0,1,0) \in \{0,1\}$ |

| 0 | 1 | 1 | $f(0,1,1) \in \{0,1\}$ |

| 1 | 0 | 0 | $f(1,0,0) \in \{0,1\}$ |

| 1 | 0 | 1 | $f(1,0,1) \in \{0,1\}$ |

| 1 | 1 | 0 | $f(1,1,0) \in \{0,1\}$ |

| 1 | 1 | 1 | $f(1,1,1) \in \{0,1\}$ |

M + N Spalten

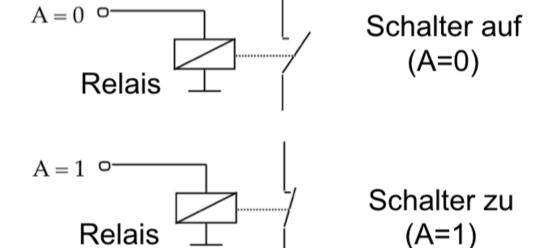

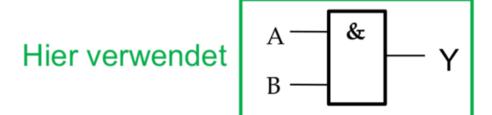

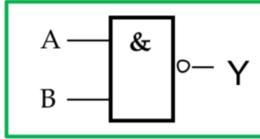

## **UND-Verknüpfung**

• Y = 1, wenn A = 1 & B = 1

| Α | В | Υ |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | O |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

$$Y = A \wedge B$$

$Y = A \cdot B$

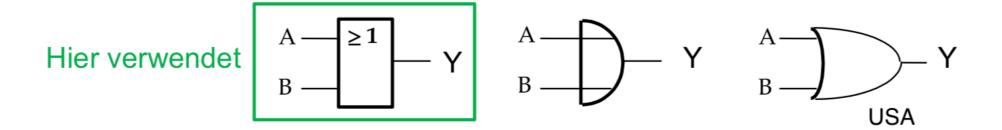

Hier verwendet

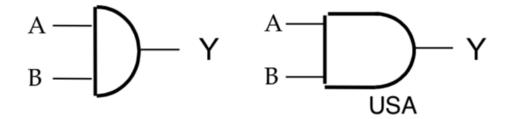

# ODER-Verknüpfung

• Y = 1, wenn A = 1 &/oder B = 1

| Α | В | Υ             |

|---|---|---------------|

| 0 | 0 | 0             |

| 0 | 1 | \( \lambda \) |

| 1 | 0 | ٨             |

| 1 | 1 | Λ             |

$$Y = A \lor B$$

$Y = A + B$

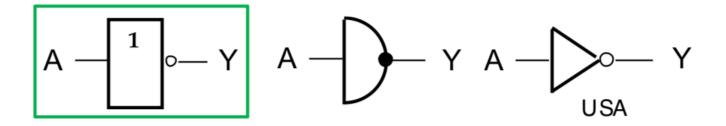

#### **INVERTER**

• Y = 1, wenn A = 0

| Α | Y        |

|---|----------|

| 0 | <b>✓</b> |

| 1 | 0        |

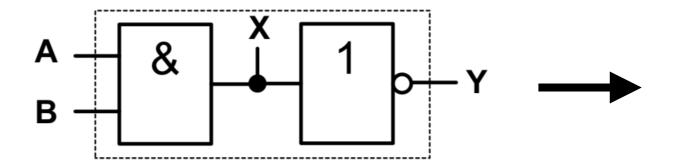

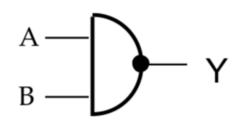

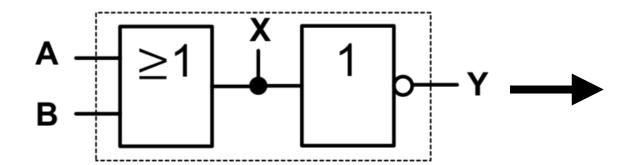

### **NAND-Gatter**

• Y = 1, wenn A = 0%/oder B = 0

| Α | В | X | Y         |

|---|---|---|-----------|

| 0 | 0 | 0 | $\lambda$ |

| 0 | 1 | 0 | ٨         |

| 1 | 0 | 0 | Λ         |

| 1 | 1 | Λ | 0         |

$$Y = \overline{A \wedge B} \qquad Y = \overline{A \cdot B}$$

Hier verwendet

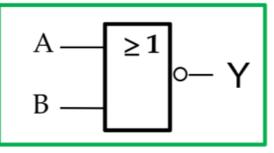

### **NOR-Gatter**

• Y = 1, wenn A = 0 & B = 0

| Α | В | X | Y |

|---|---|---|---|

| 0 | 0 | 0 | 1 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | Λ | 0 |

$$Y = \overline{A \vee B}$$

$$Y = \overline{A + B}$$

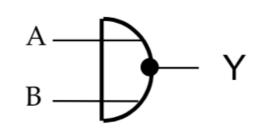

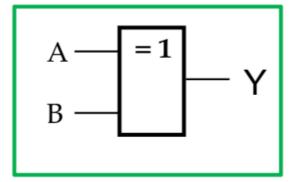

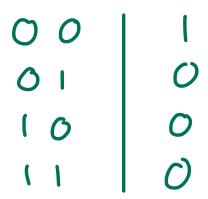

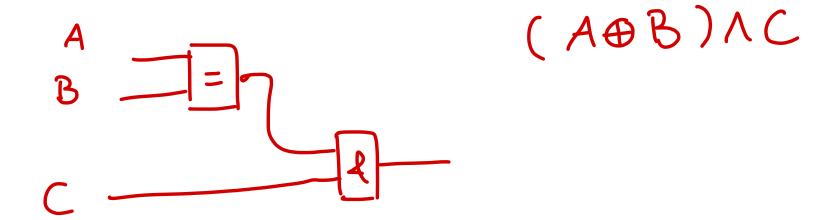

# XOR-Gatter (= Exclusive Or)

• Y = 1, wenn A = 0 oder B = 0

| Α | В | X |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

Hier verwendet

Hier verwendet

$$Y = A \oplus B$$

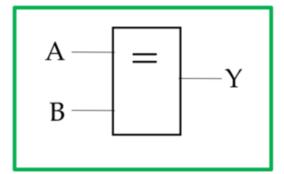

#### **XNOR-Gatter**

Invertiertes XOR-Gatter

$$Y = \overline{A \oplus B}$$

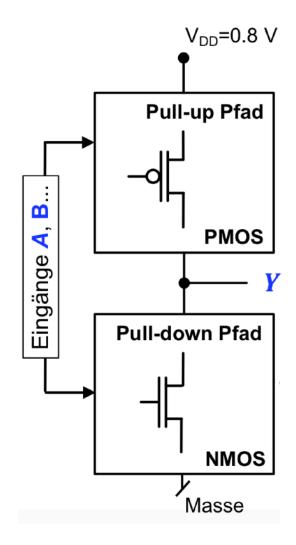

# CMOS Schaltungen

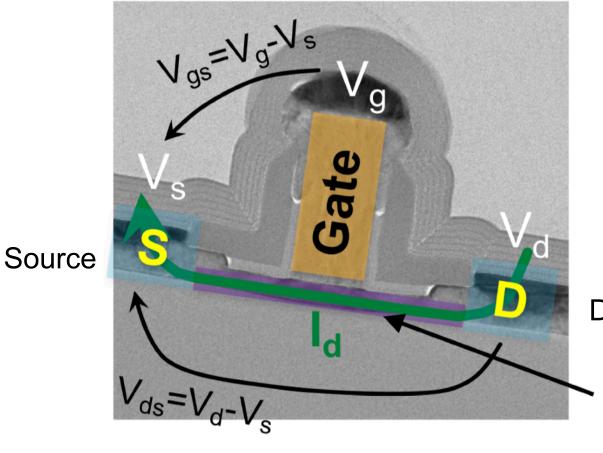

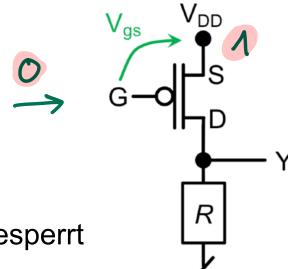

#### **MOS-Transistoren**

- |V\_gs| < |V\_th| kein Strom fliesst

- |V\_gs| > |V\_th| es fliesst Strom

- |V\_th| = Schwellenspannung (ca. 0.8V)

- Funktioniert durch Halbleiter

Drain

R<sub>T</sub> (Halbleiter)

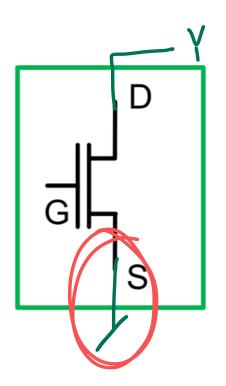

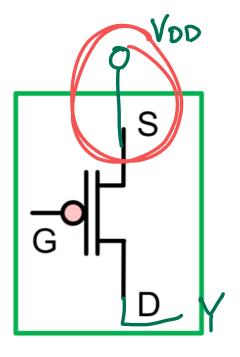

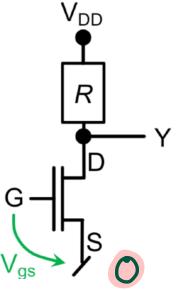

### **NMOS**

- Elektronen fliessen von S zu D

- P-Typ Halbleiter

- Für Pull-down Schaltung verwendet

### **PMOS**

- Löcher fliessen von S zu D

- N-Typ Halbleiter

- Für Pull-up Schaltung verwendet

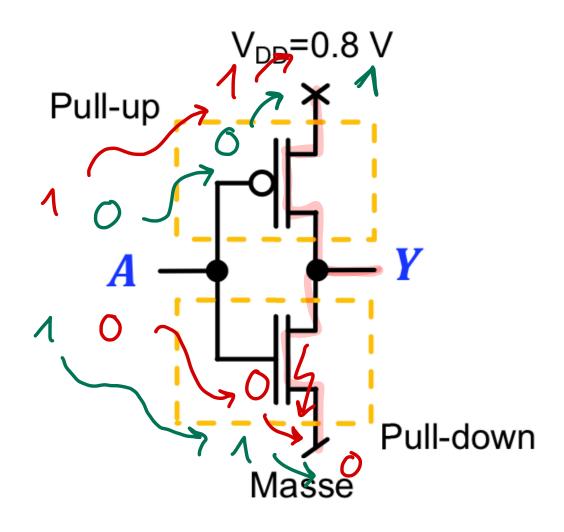

## Pull-up Schaltung

- PMOS-Transistoren

- Leitet, wenn G != S (G = 0)

- Leitet eine 1 weiter (an V\_DD gebunden)

- NN (Unbestimmter Zustand) wenn Transistor davor gesperrt

## Pull-down Schaltung

- NMOS-Transistoren

- Leitet, wenn G != S (G = 1)

- Leitet eine 0 weiter (an Masse gebunden)

- NN (Unbestimmter Zustand) wenn Transistor davor gesperrt

# Schaltungen

• # NMOS-Transistoren = # PMOS-Transistoren = # Eingänge

# NOT

| A | PMOS  | NMOS  | Y |

|---|-------|-------|---|

| 0 | ZU    | OFFEN | Λ |

| 1 | OFFEN | ZU    | 0 |

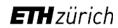

## **NAND**

- PMOS parallel

- NMOS in Serie

**NOR**

$V_{DD} = 0.8 V$

- PMOS in Serie

- NMOS parallel

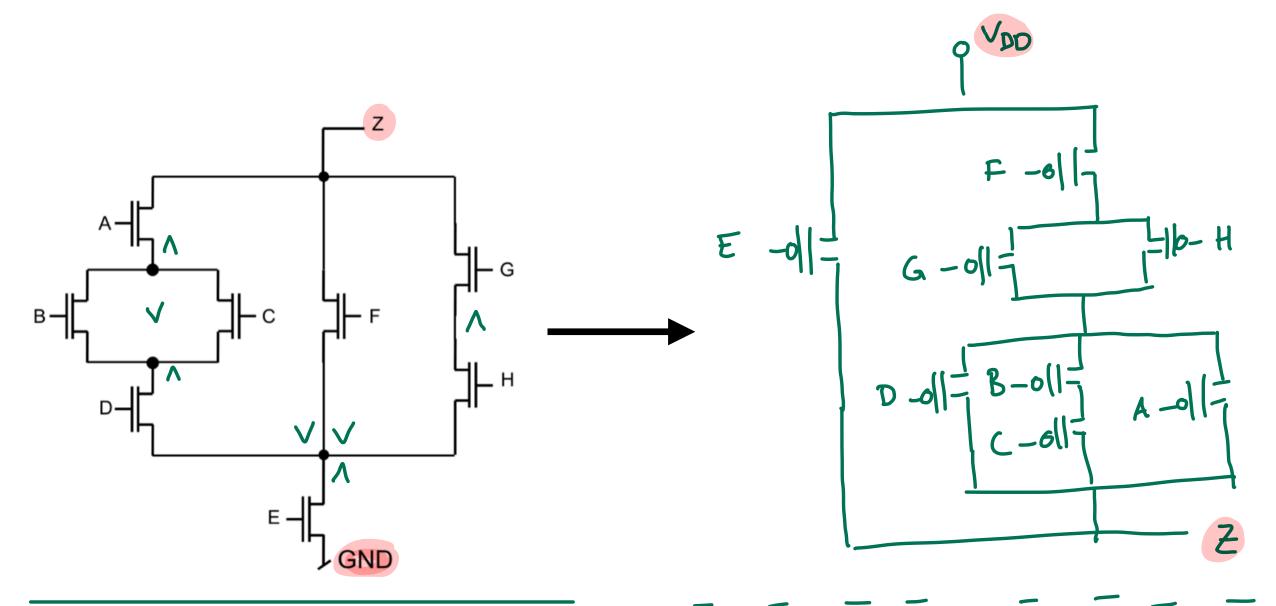

#### Pfade umwandeln

- 1. Gleichung aufstellen

- (Bei Pull-up einzelne Elemente invertiert, bei Pull down ganze Gleichung)

- (UND in Serie, ODER parallel)

- 2. Gleichung invertieren

**ETH** züric

- (UND/ODER vertauschen und Investierungen vertauschen)

- 3. Neue Gleichung zeichnen

- (UND: Serie, ODER: Parallel)

EN (FV (GNH) V (DN (BVC) NA)) -> EV (FN (GVH) N (DV (BNC) VA)

**ETH** zürich

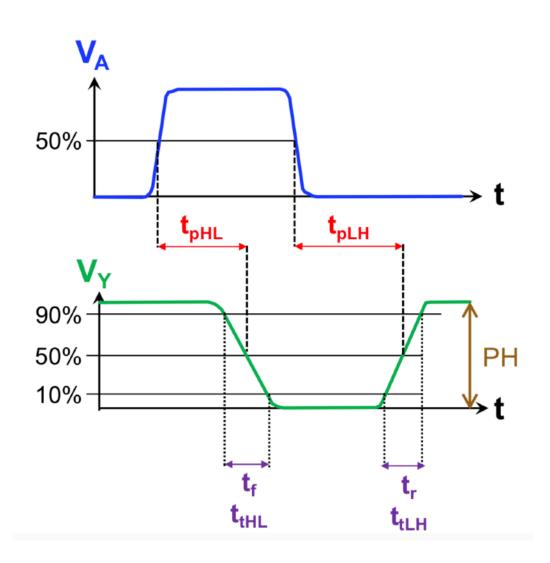

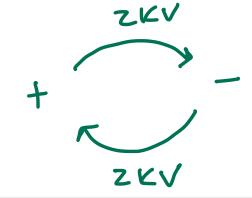

# Zeitverzögerung

$$t_d = (t_{pHL} + t_{pLH})/2$$

- Verzögerungszeit, gemessen bei 50%

- "Verschiebung im Block"

- Anstiegs- Abfallszeit, gemessen bei 10%-90%

- "Schräge Übergänge"

# Zeitverzögerung

Schritt 1: Signal ohne Zeitverzögerung einzeichnen

# Bool'sche Algebra

# Basisregeln Schaltalgebra

- Kommutativität: (A + B + C = B + C + A) (A \* B \* C = B \* A \* C)

- Assoziativität: (A + (B + C) = (A + B) +C) (A \* (B \* C) = (A \* B) \* C)

- Distributivität: (A \* B + A \* C = A \* (B + C)) ((A + B) \* (A + C) = A + (B \* C))

- "Normale" Regeln für Multiplikation und Addition

# Bool'sche Grundregeln

| NICHT         | !!A = A                | -                      |

|---------------|------------------------|------------------------|

| NULL          | A + 0 = A              | A * 0 = 0              |

| EINS          | A + 1 = 1              | A * 1 = A              |

| IDEMPOTENZ    | A + A = A              | A * A = A              |

| KOMPLEMENT    | A + !A = 1             | A * !A = 0             |

| ADSORPTION    | A + (!A * B) = A + B   | A * (!A + B) = A * B   |

| ABSORPTION    | A + (A * B) = A        | A * (A + B) = A        |

| NACHBARSCHAFT | (A * B) + (!A * B) = B | (A + B) * (!A + B) = B |

## Vorrangsregeln

- Klammern

- {AND; OR; NOR; NAND} vor {XOR; XNOR}

- {AND; OR; NOR; NAND} und {XOR; XNOR} sind untereinander gleichwertig

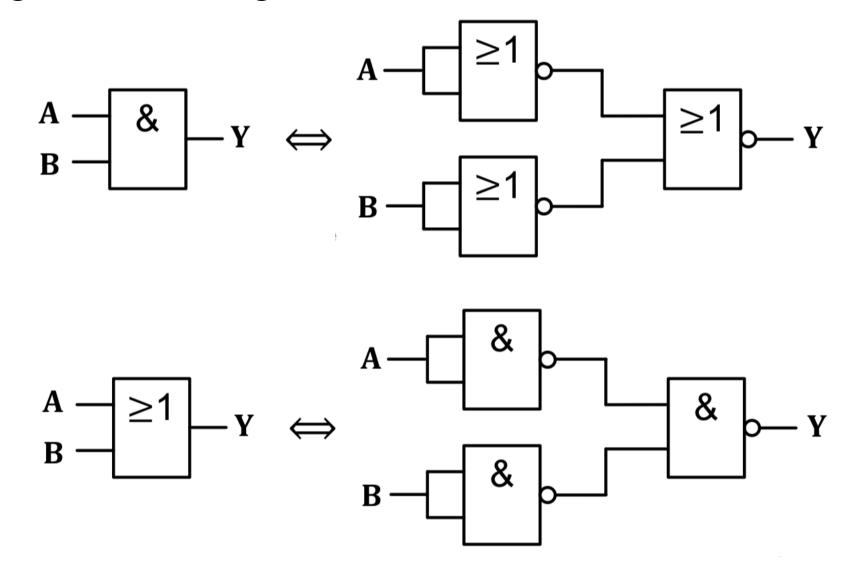

# De Morgan'sche Regeln

Die De Morgan'schen Gesetze sind verallgemeinerbar auf mehreren Variablen:

Erstes Gesetz:  $Y = \overline{A \wedge B \wedge C \wedge \cdots} = \overline{A} \vee \overline{B} \vee \overline{C} \vee \cdots$

Zweites Gesetz:  $Y = \overline{A \vee B \vee C \vee \cdots} = \overline{A} \wedge \overline{B} \wedge \overline{C} \wedge \cdots$

# De Morgan'sche Regeln

# Schaltungssynthese

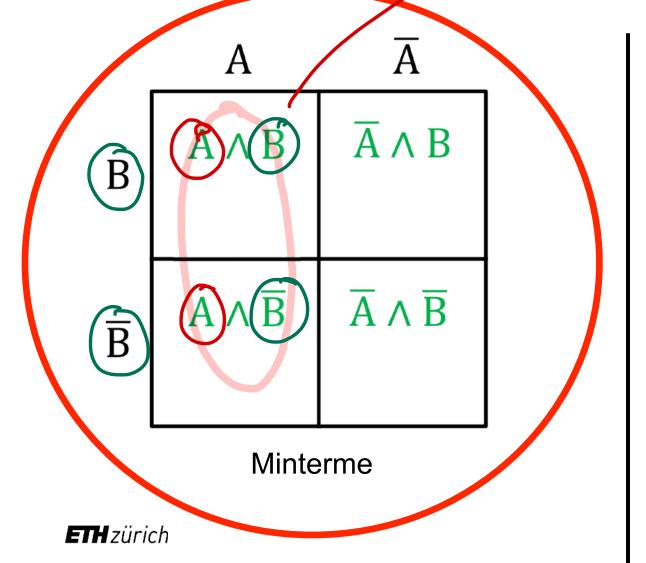

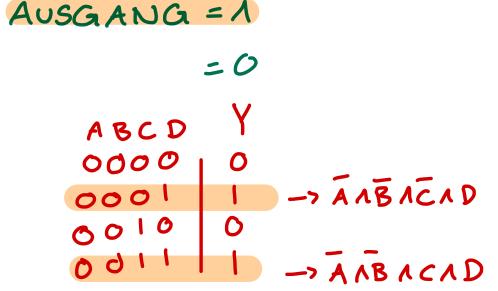

#### **Minterm**

- UND-Verknüpfung von Schaltvariablen

- Minterm gibt nur bei einer Variablenkombination 1 (Minimum)

- Bei n Variablen 2<sup>n</sup> Minterme

- Bildung und Variablenfindung:

- Invertierte = 0

- Nicht-invertierte = 1

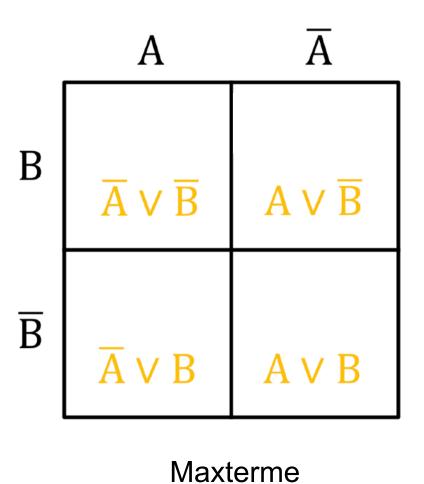

#### Maxterm

- ODER-Verknüpfung von Schaltvariablen

- Maxterm gibt nur bei einer Variablenkombination 0 (Maximum)

- Bei n Variablen 2<sup>n</sup> Maxterme

- Bildung und Variablenfindung:

- Invertierte = 1

- Nicht-invertierte = 0

#### Normalformen

## Disjunktive Normalform

ODER-Verknüpfung von allen Mintermen = 1

## Konjunktive Normalform

• UND-Verknüpfung von allen Maxtermen = 0

#### Kanonische Form

• Nur Min- oder Maxterme mit jeder Variable genau 1 Mal

| Α | В | С | Y = f(A, B, C) | Minterm   | Maxterm |

|---|---|---|----------------|-----------|---------|

| 0 | 0 | 0 | 1              | A N B N こ |         |

| 0 | 0 | 1 | 1              | ĀNBAC     |         |

| 0 | 1 | 0 | 0              |           | AVBVC   |

| 0 | 1 | 1 | 1              | ANBAC     |         |

| 1 | 0 | 0 | 1              | ANBAC     |         |

| 1 | 0 | 1 | 1              | ANBAC     |         |

| 1 | 1 | 0 | 0              |           | AVBVC   |

| 1 | 1 | 1 | 0              |           | AVBVC   |

DNF: (AABAC)V(AABAC)V(AABAC) V(AABAC)

KNF: (AVBVC) M(AVBVC) M(AVBVC)

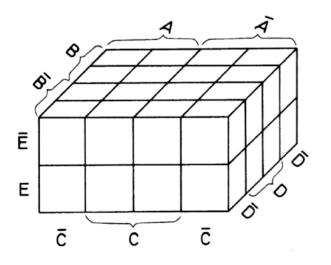

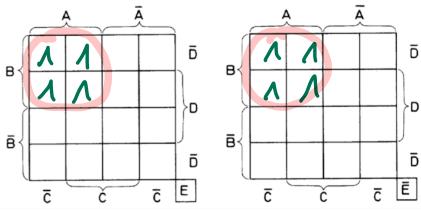

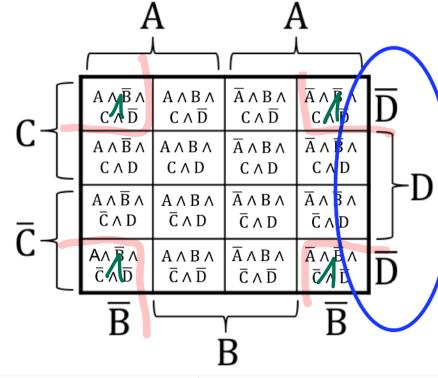

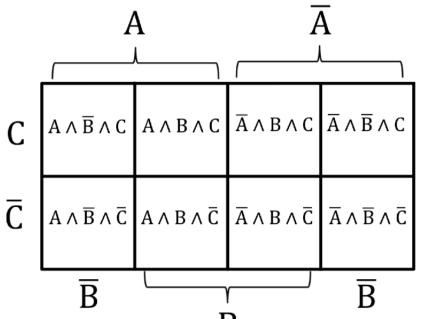

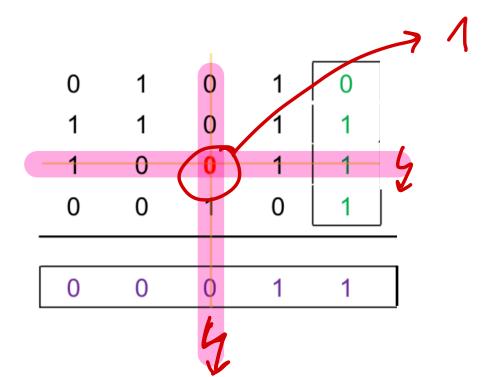

## Karnaugh Diagramme

Zum vereinfachen der Kanonischen Formen

## Vereinfachen mit dem Karnaugh Diagramm (DNF)

- 1 eintragen, wenn der Minterm existiert.

- 0 eintragen, wenn der Minterm nicht existiert.

- Päckchen können gebildet werden, wenn:

- mind. eine Variable negiert und nicht negiert vorkommt

- mind, eine Variable konstant bleibt

- Felder könne zu mehreren Päckchen gehören

- Aufgeschrieben wird die Variable, die konstant bleibt

## Mehr Variablen möglich...

$f = (\overline{B} \wedge \overline{C}) \vee (A \wedge \overline{B}) \vee (A \wedge B \wedge \overline{C}) \vee (A \wedge \overline{B} \wedge C \wedge \overline{D}) \vee (\overline{A} \wedge \overline{B} \wedge \overline{C} \wedge \overline{D})$ A I II III (AAB) V (BAC) I 亚 亚 (BVA) A (CCVB) A (CCVA) B

## Vereinfachung mit der KNF

- 0-Päckchen

- Maxterme formen und mit UND verknüpfen

- Eingänge invertieren

- Siehe Serie

#### Don't Care Zustände

- Nicht benutzte Zustände können im Karnaugh Diagramm mit X gekennzeichnet werden.

- X können bei der Päckchenbildung mitbenutzt werden.

$$2^{2} = 4$$

$$2^{3} = 8 \times 12 \text{ gebrauchte} + 4 \text{ umbeuntete}$$

$$2^{4} = 16 \times 12 \text{ gebrauchte}$$

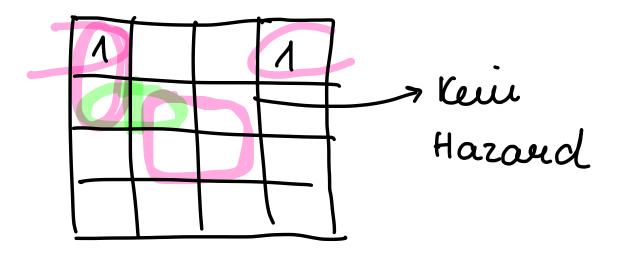

#### Hazards

- Durch Zeitverzögerung

- Bei Päckchen, die sich orthogonal berühren

- Behebung: Zusätzliches Päckchen um die betroffenen Stellen

## Zahlen & Codes

## Zahlensysteme Definition (Das Dezimalsystem)

T H Z E

3 5 7

$$D = \sum_{i=-\infty}^{i=\infty} b_i \cdot R^i$$

Zwischen 0 und R-1

357 = 7 \* 1 + 5 \* 10 + 3 \* 100 = 3 \* 10^0 + 5 \* 10^1 + 3 \* 10^2

## Gebräuchliche Zahlensysteme

- Dezimal

- Basis = 10

- Binär (0b)

- Basis = 2

- Hexadezimal (0x)

- Basis = 16

- b = {0, 1, 2, 3, 4, 5, 6, 7, 8, 9, A, B, C, D, E, F}

- Oktal (0o)

- Basis = 8

## Umwandlung Dezimal zu System mit Basis R

- Ganze Zahl

- Division mit R

- Rest eintragen (von Rechts nach Links)

- Quotient wieder Teilen bis dieser == 0

- Zahl zwischen 0 und 1

- Mit R Multiplizieren

- Zahl vor dem Komma eintragen (von Links nach Rechts)

- Zahl vor dem Komma wegnehmen und wieder Multiplizieren bis ganze Zahl

## Beispiel Dezimal zu System mit Basis R

21

10 R1

5

2 R1

1

ORA

0b 101010

00 52

0x 2 A

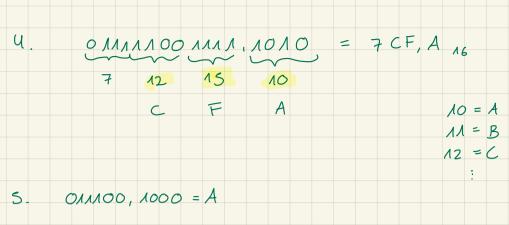

## Umwandlung Binär zu Hex

- Viererpäckchen bilden (von hinten aus)

- Viererpäckchen umwandeln in Dezimal

- Zahlen >9 als Buchstaben schreiben und alles als Hex schreiben

## Umwandlung Binär zu Oct

- Dreierpäckchen bilden (von hinten aus)

- Dreierpäckchen umwandeln in Dezimal

- Als Oct schreiben

### Beispiel Binär zu Hex

$$A = AO$$

$B = AA$

$C = A2$

Beispiel Binär zu Oct

$$200 = 0011001000 = 00 310$$

$$= 3 = 1$$

#### Binärzahlen addieren

"Normales" schriftliches addieren

$$A + A = 2 = (A \circ)_2$$

$$3 = (A \wedge)_2$$

1 1 1 1 1 1

$$0 1 1 0 0 1 1$$

+ 1 1 1 0 1 1 1 0 0

= 1 0 1 0 1 0 0.1 1 1

#### Binärzahlen subtrahieren

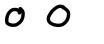

- Negatives Zweierkomplement zur zu subtrahierenden Zahl bilden

- "Normales" schriftliches addieren

## Zweierkomplement

• Um negative Dualzahlen darstellen zu können

|         | VZ | Betrag                                                                                           |

|---------|----|--------------------------------------------------------------------------------------------------|

| positiv | 0  | $MSB, MSB_{-1}, MSB_{-2}, \cdots, LSB =  X_{(2)} $                                               |

| negativ | 1  | $\rightarrow  X_{(2)} $ Bitweise invertieren                                                     |

|         |    | $ ightarrow$ Eine $1_{(2)}$ muss an der LSB Stelle addiert werden                                |

|         |    | $\overline{MSB}$ , $\overline{MSB_{-1}}$ , $\overline{MSB_{-2}}$ ,, $(\overline{LSB} + 1_{(2)})$ |

$$42 = \frac{00000000}{1000000}$$

$$+ \frac{1000000}{100000}$$

$$-42 = \frac{100000000}{10000000}$$

(8 Stellen)

## Binärzahlen subtrahieren – Beispiel

#### Codes

Einzelne Ziffern in Binärdarstellung

| Binär | BCD | Excess-3 | Aiken | 4-2-2-1 | Gray | O'Brien |

|-------|-----|----------|-------|---------|------|---------|

| 0000  | 0   |          | 0     | 0       | 0    |         |

| 0001  | 1   |          | 1     | 1       | 1    |         |

| 0010  | 2   |          | 2     | 2       | 3    | 0       |

| 0011  | 3   | 0        | 3     | 3       | 2    |         |

| 0100  | 4   | 1        | 4     |         | 7    | 4       |

| 0101  | 5   | 2        |       |         | 6    | 3       |

| 0110  | 6   | 3        |       | 4       | 4    | 1       |

| 0111  | 7   | 4        |       | 5       | 5    | 2       |

| 1000  | 8   | 5        |       |         |      |         |

| 1001  | 9   | 6        |       |         |      |         |

| 1010  |     | 7        |       |         |      | 9       |

| 1011  |     | 8        | 5     |         |      |         |

| 1100  |     | 9        | 6     | 6       | 8    | 5       |

| 1101  |     |          | 7     | 7       | 9    | 6       |

| 1110  |     |          | 8     | 8       |      | 7       |

| 1111  |     |          | 9     | 9       |      | 8       |

Beim Zählen verändert sich immer nur eine Zahl

## Fehlererkennung

- 61010 11011 1011 00101

- Code wird in regelmässigen Abständen (Tetrade) um ein Parity Bit ergänzt

- 00011

- Even Parity Bit = 0 wenn Anzahl 1 gerade

- Odd Parity Bit = 0 wenn Anzahl 1 ungerade

- Am Ende des übertragenen Codes wird ein Prüfwort angehängt

# Rechenschaltungen

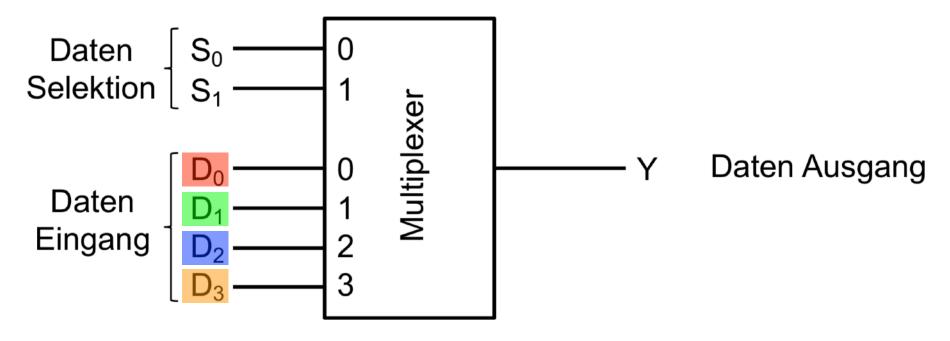

## Multiplexer

#### Mehrere Eingänge auf einen Ausgang

$$Y = (\overline{S_0} \wedge \overline{S_1} \wedge \overline{D_0}) \vee (\overline{S_0} \wedge S_1 \wedge \overline{D_1}) \vee (S_0 \wedge \overline{S_1} \wedge \overline{D_2}) \vee (S_0 \wedge S_1 \wedge \overline{D_3})$$

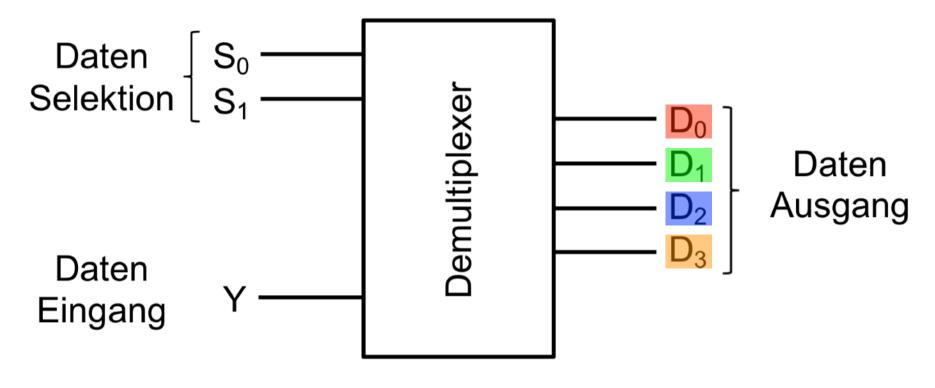

## Demultiplexer

#### Ein Eingang auf mehrere Ausgänge

$$D_0 = \overline{S_0} \wedge \overline{S_1} \wedge Y, \qquad D_1 = \overline{S_0} \wedge S_1 \wedge Y,$$

$$D_2 = S_0 \wedge \overline{S_1} \wedge Y$$

,  $D_3 = S_0 \wedge S_1 \wedge Y$

$$D_1 = \overline{S_0} \wedge S_1 \wedge Y_1$$

$$D_3 = S_0 \wedge S_1 \wedge Y$$

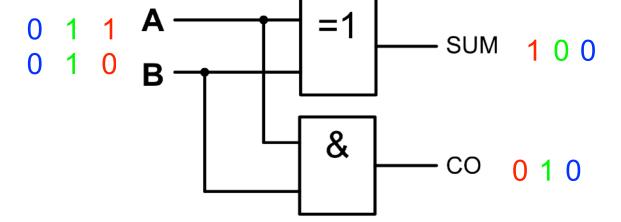

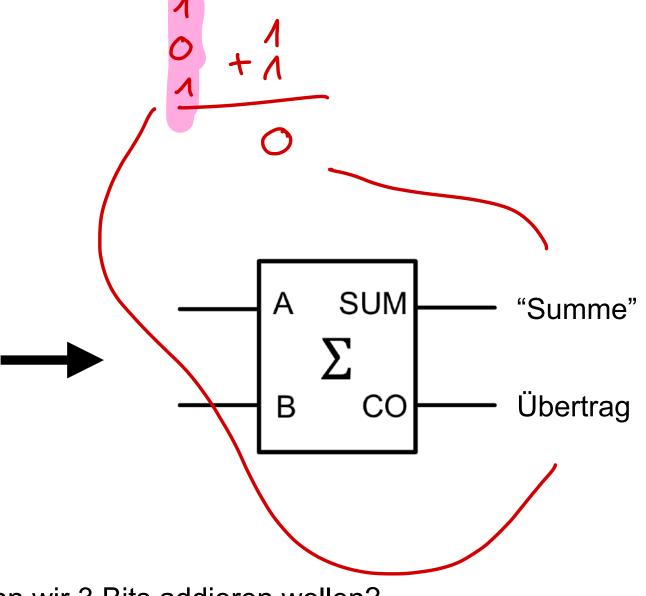

#### Halbaddierer

• Um 2 Bits zu addieren

Was machen wir, wenn wir 3 Bits addieren wollen?

#### Volladdierer

- Um 3 Bits zu addieren

- A + B + C = (A + B) + C

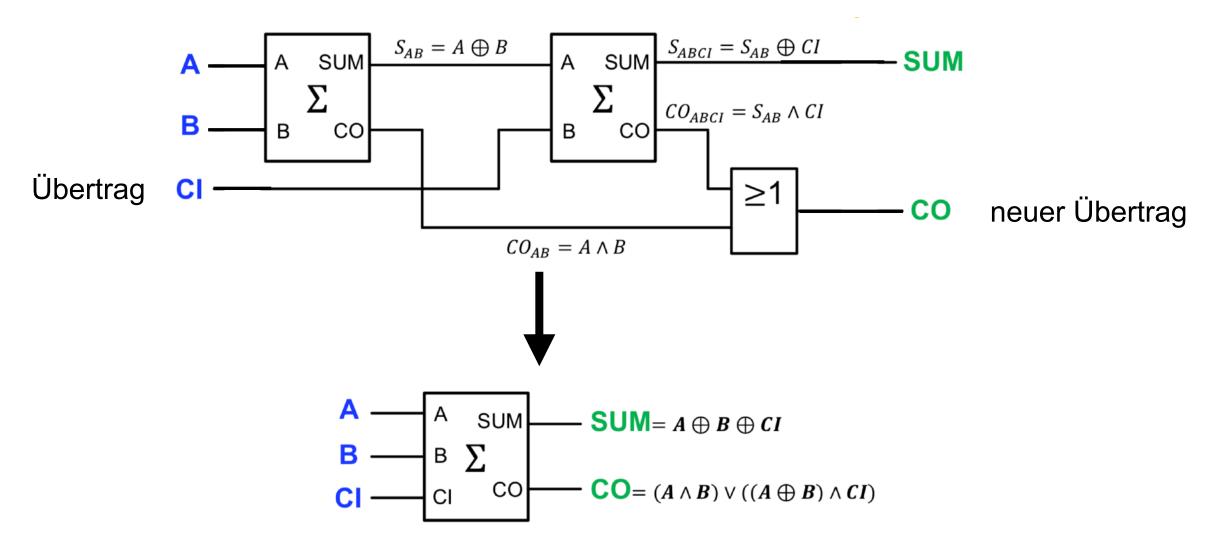

#### Mehrbit-Addierer

- Wir wollen ganze Dualzahlen addieren

- Serienaddierer: in jedem Taktschritt wird eine Stelle addiert

- Paralleladdierer: in einem Taktschritt werden alle Stellen addiert

#### Paralleladdierer

• Für jedes Bit eine Schaltung generieren

•

$$S_0 = A_0 + B_0$$

- Vorteile

- Schnell, da die Daten max. durch 3 Gatter müssen

- Nachteile

- sehr Schaltungsaufwendig

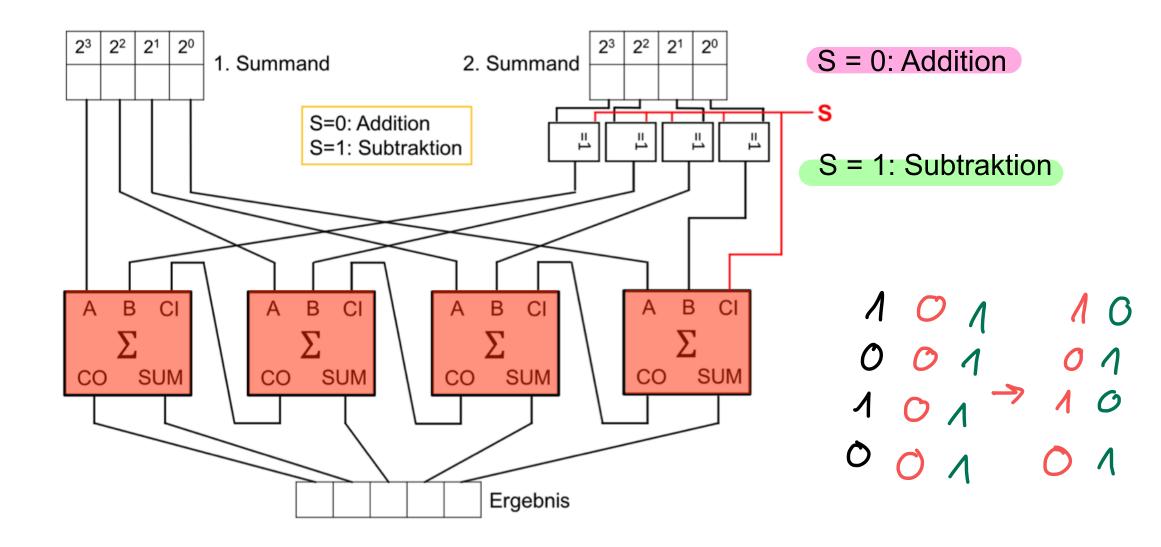

## Ripple-Carry Addierer

## Ripple-Carry Addierer II

- Vorteile

- Schaltungsaufwand wächst linear

- Einfach erweiterbar

- Nachteile

- langsam, da die Daten durchrieseln müssen

## Carry-Lookahead Addierer

- Addierer werden kaskadiert

- Überträge werden parallel berechnet

- Vorteile

- Gleich schnell wie der Paralleladdierer

- Schaltungsaufwand wächst linear (wie bei Ripple-Carry)

#### Subtrahierer

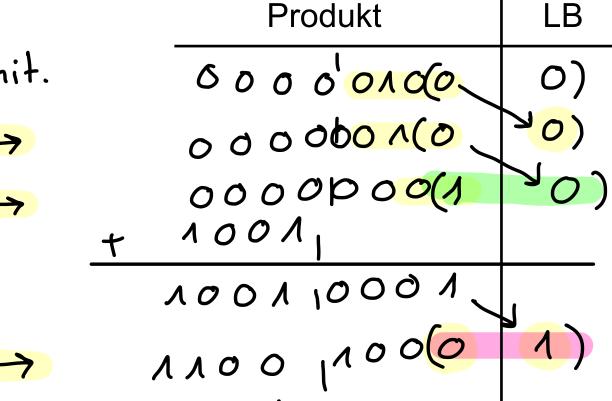

#### A.B Multiplikation von Binärzahlen Multiplikator 1.75 (b) 1.875 Multiplikand (a) 1. Übertrag Überträge 2. Übertrag 3. Übertrag $b_0 \cdot \boldsymbol{a}$ 0 $b_1 \cdot \boldsymbol{a}$ 4. Übertrag $b_2 \cdot \boldsymbol{a}$ 0 0 $b_3 \cdot \boldsymbol{a}$ 0 3.2812 0 3+3=6 Nachkommastellen

**ETH** zürich

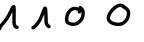

## **Booth-Algorithmus**

$$A = 10 10$$

$$B = 111$$

$$= 0111$$

$$(1\ 0)$$

: -B

$$(0\ 1)$$

: +B

Shift

$$A = 0100$$

$$B = 0111$$

$$-B = 1001$$

# Latches & Flipflops

## Kombinatorische Schaltungen

- Ausgang hängt nur von den Eingängen und Gattern ab

- Bisher nur solche betrachtet

## Sequentielle Schaltungen

- Besitzen Rückkoppelungen

- jetzt neu

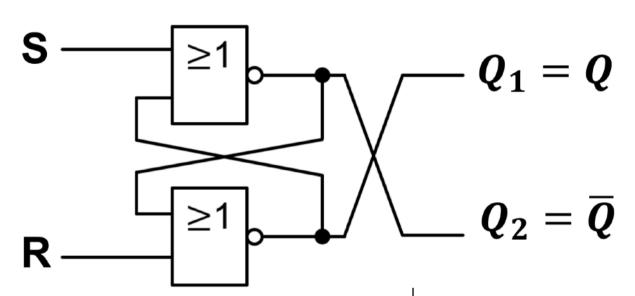

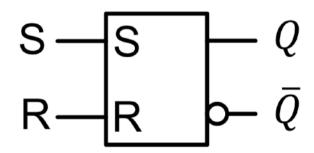

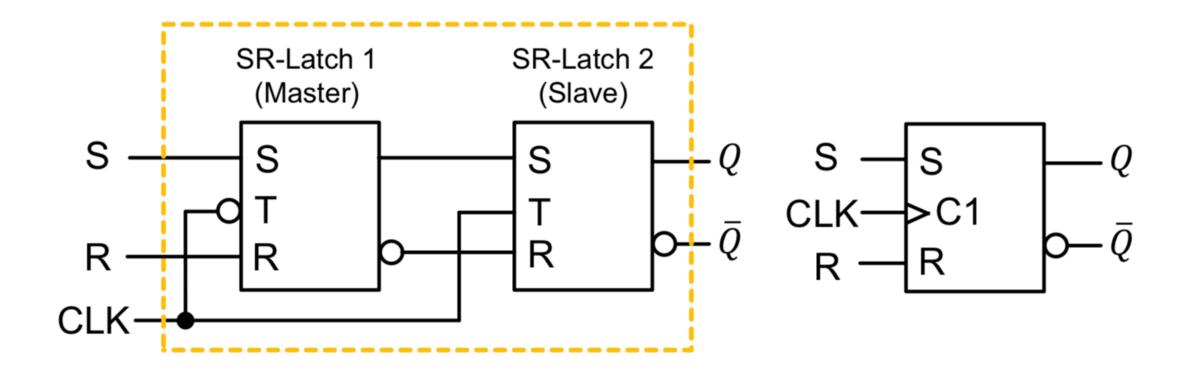

### **SR-Latch**

| Fall | S | R | $Q_{1n}$ | $Q_{1n+1}$ |

|------|---|---|----------|------------|

| 1    | 0 | 0 | 0        | 0          |

| 2    | 0 | 0 | 1        | 1          |

| 3    | 0 | 1 | 0        | 0          |

| 4    | 0 | 1 | 1        | 0          |

| 5    | 1 | 0 | 0        | 1          |

| 6    | 1 | 0 | 1        | 1          |

| 7    | 1 | 1 | 0        | X          |

| 8    | 1 | 1 | 1        | X          |

speichern

rücksetzen

setzen

unzulässig

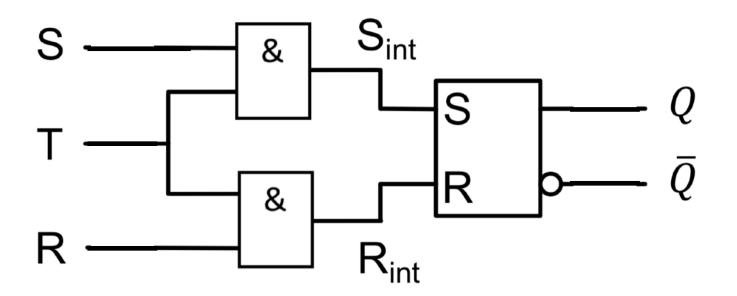

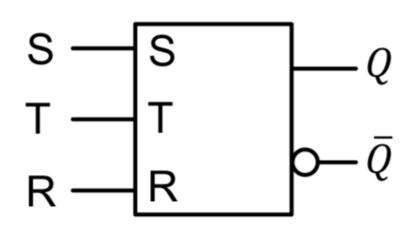

## Taktzustandgesteuertes SR-Latch

Gleich wie SR-Latches, nur dass sich Q nur verändern kann, wenn T = 1

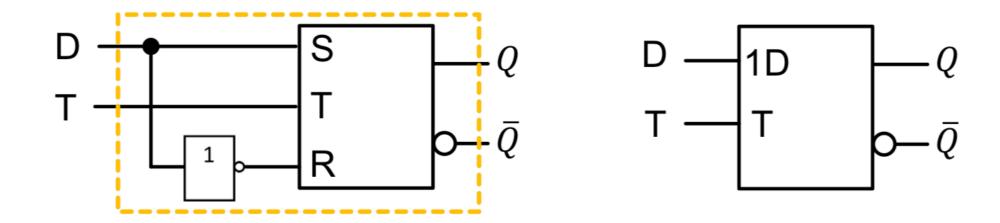

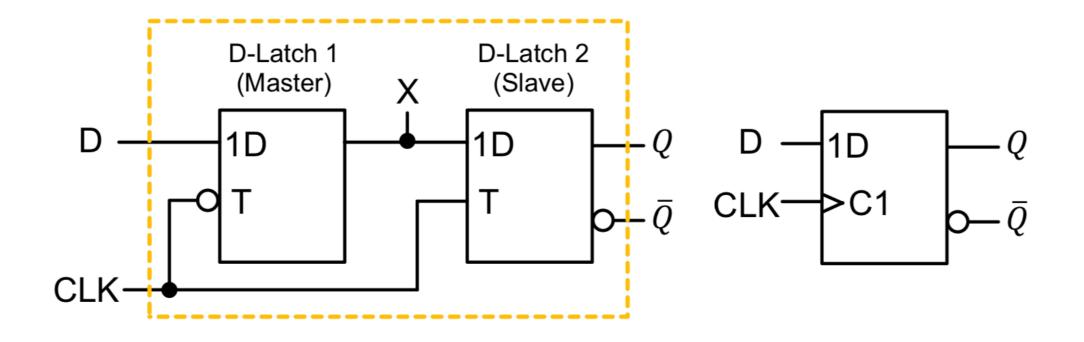

#### **D-Latches**

- Die Eingangskombination R = S = 1 wird verhindert

- Q = D während T = 1

- Bei T = 0 wird der letzte Wert vor dem Übergang beibehalten

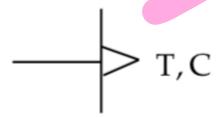

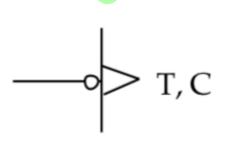

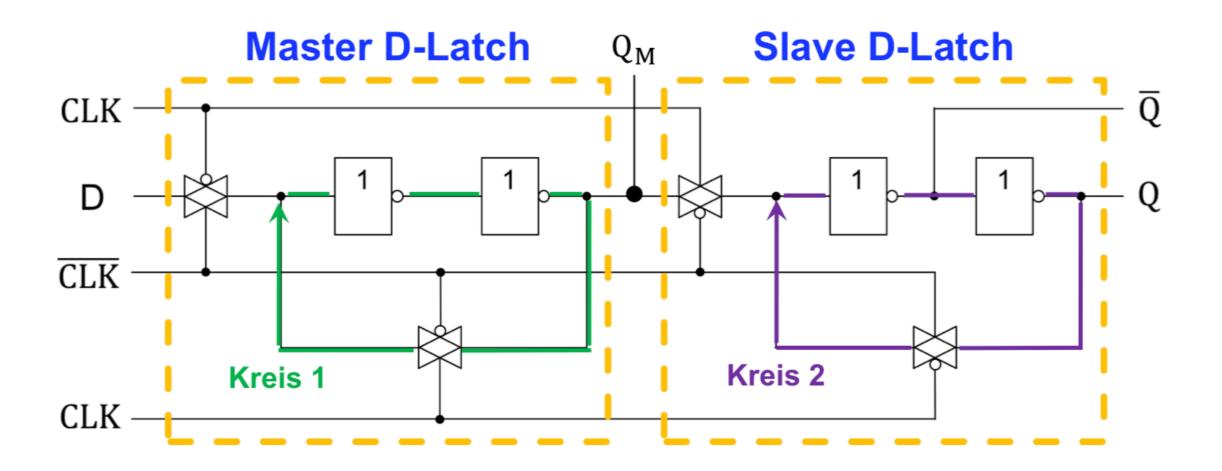

## Flipflops

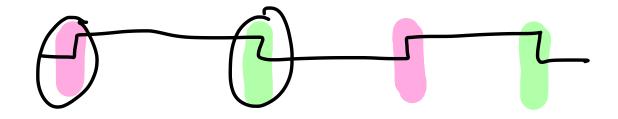

TaktFLANKENgesteuert

Eingangsvariable werden beim 0 - 1 Übergang von C wirksam

Eingangsvariable werden beim 1 - 0 Übergang von C wirksam

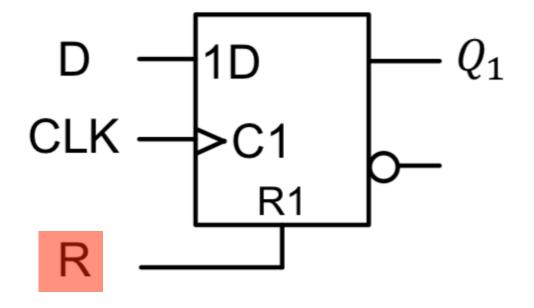

#### **D-Flipflop**

Ausgang wird zu D bei jeder positiven Taktflanke

## SR-Flipflop

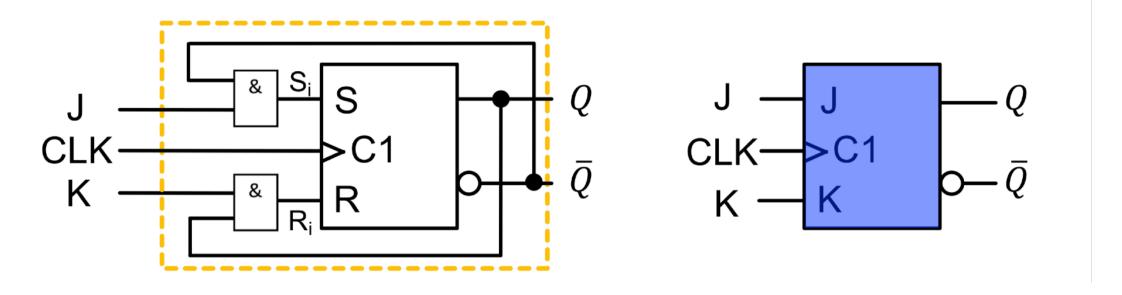

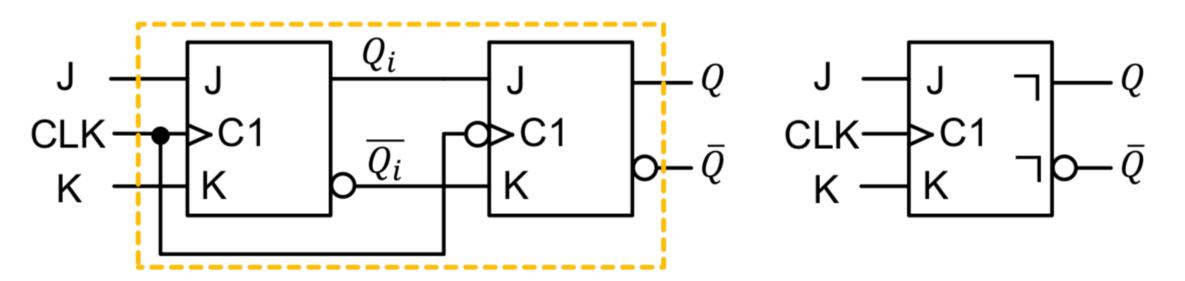

## JK-Flipflop (Jump - Kill)

| Fall | J | K | $Q_{1n+1}$          | $Q_{2n+1}$          |

|------|---|---|---------------------|---------------------|

| 1    | 0 | 0 | $Q_{1n}$            | $Q_{2n}$            |

| 2    | 0 | 1 | 0                   | 1                   |

| 3    | 1 | 0 | 1                   | 0                   |

| 4    | 1 | 1 | $\overline{Q_{1n}}$ | $\overline{Q_{2n}}$ |

speichern rücksetzen setzen wechseln

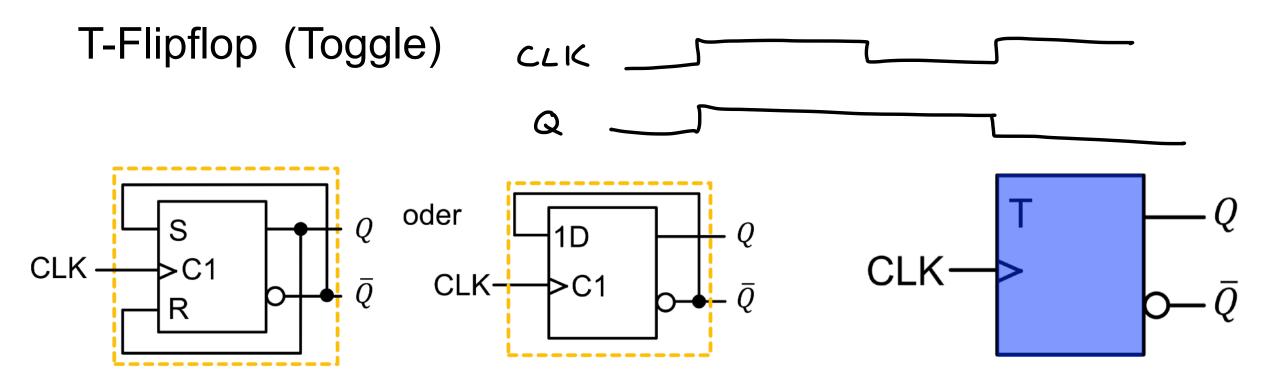

Signal "toggelt" (= wechselt) bei jeder Taktflanke

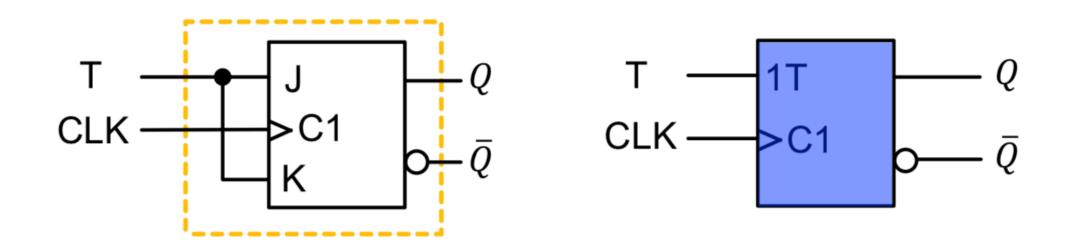

## T-Flipflop mit 2 Eingängen

Signal "toggelt" nur, wenn T = 1

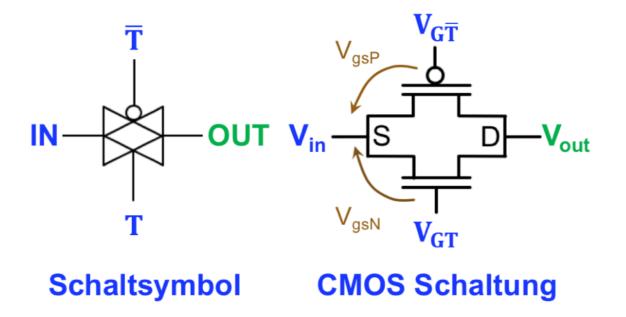

#### **Transmission Gate**

| IN | Т | Widerstand  | OUT |

|----|---|-------------|-----|

| 0  | 0 | hochohmig   | -   |

| 0  | 1 | niederohmig | 0   |

| 1  | 0 | hochohmig   | -   |

| 1  | 1 | niederohmig | 1   |

PMOS leitet, wenn Vs = 1 und Vg = 0

NMOS leitet, wenn Vs = 0 und Vg = 1

#### D-Flipflop mit Transmission Gates

#### Rücksetz-Eingang

Speicherzustand kann jederzeit auf 0 zurückgesetzt werden

## Master-Slave Flipflop

Informationen werden bei steigender Taktflanke eingelesen aber erst bei fallender ausgegeben

#### Maximale Taktfrequenz

- [ ....

- Wenn mindestens 2 Flipflops in Serie

- t\_pd = Verzögerungszeit (Durchlaufzeit)

- t\_s = Setup-Zeit (Wie lange ein Signal vor einer Taktflanke unverändert sein muss)

- t\_h = Hold-Zeit (Wie lange ein Signal nach einer Taktflanke unverändert sein muss)

$$T_{min} - t_{s,ff2} \ge t_{pd,ff1} + t_{pd,ks}$$

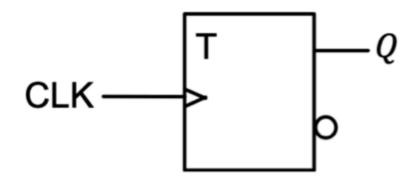

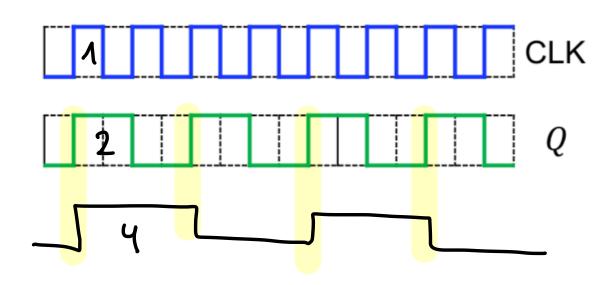

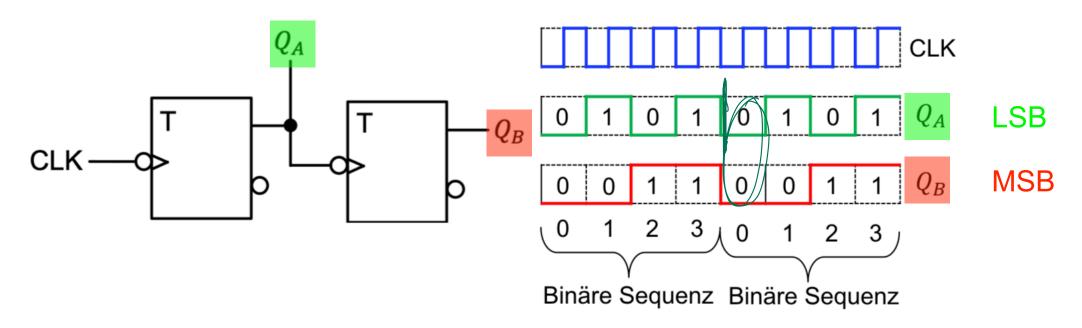

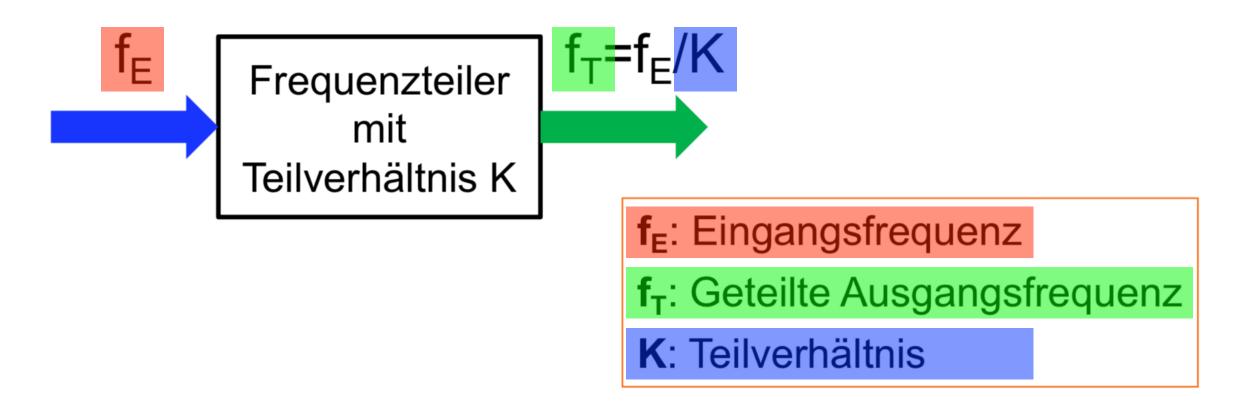

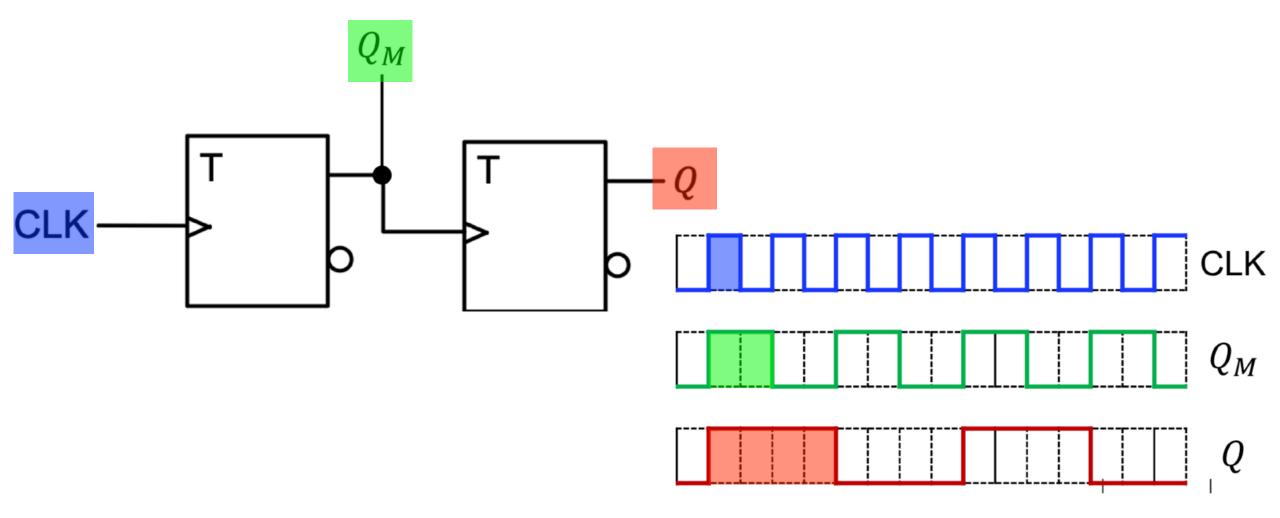

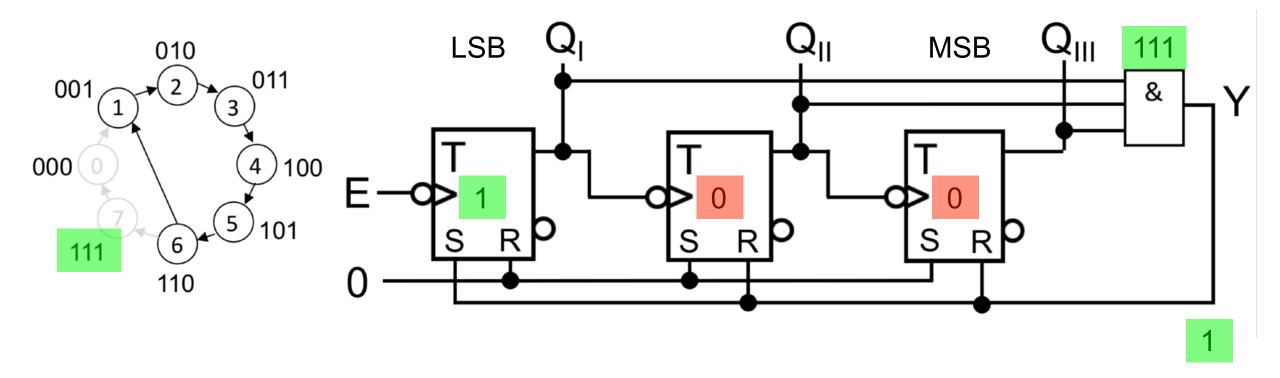

## Frequenzteiler

- T-Flipflops oder J-K-Flipflops mit J = K = 1

- n Flipflops in Serie führen zu einer Reduktion um 2<sup>n</sup>

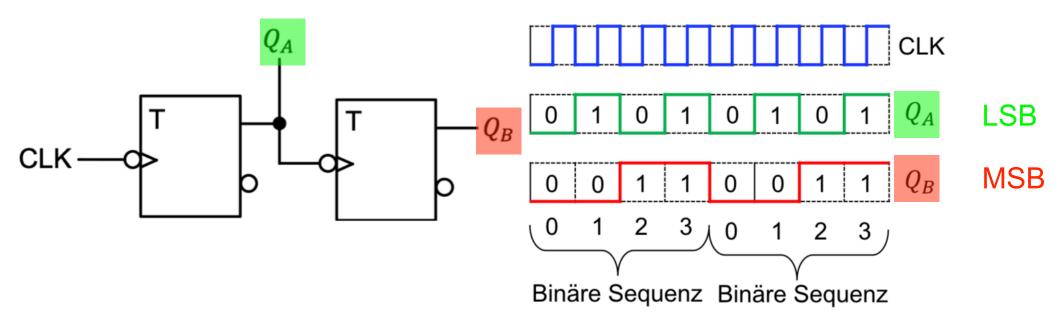

#### Dualzähler

- T-Flipflops oder JK-Flipflops mit J = K = 1

- Bei n Flipflops Zahlen bis 2<sup>n</sup> 1

## Automaten

#### Automaten

Hier nur synchrone Automaten betrachtet (alle FF haben das gleiche Taktsignal)

#### Finite State Machine (= Endliche Automaten)

- mögliche Eingabezeichen

- mögliche Ausgabezeichen

- intern gespeicherte Zustände

sind endlich

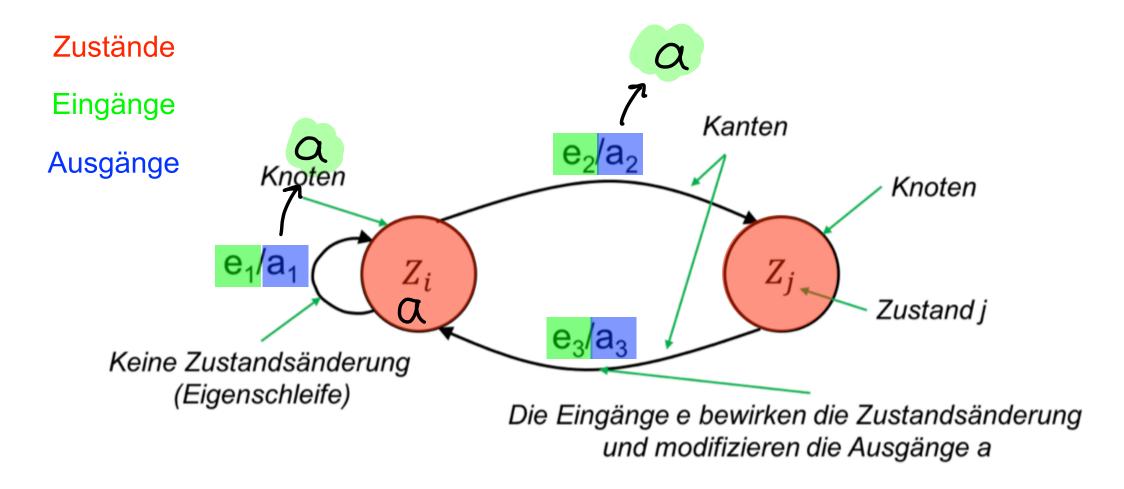

#### Beschreibung von Automaten

- X = Eingabealphabet

- Y = Ausgabealphabet

- Z = Zustandsmenge

- Z\_0 = Anfangszustand

- F\_c1 = Übergangsfunktionen

- F\_c2 = Ausgangsfunktionen

#### Mealy - Automat

- Ausgang von Eingang und internem Zustand abhängig

- $Y_n = f_{C2}(X_n, Z_n)$  $Z_{n+1} = f_{C1}(X_n, Z_n)$

#### Moore - Automat

- Sonderfall vom Mealy-Automat

- Ausgang hängt nur vom internen Zustand ab

- $Y_n = f_{C2}(Z_n)$   $Z_{n+1} = f_{C1}(X_n, Z_n)$

- Medwedjew-Automat, wenn Ausgang = interner Zustand ( $Y_n = Z_n$ )

## Zustandsfolgetabelle

$$n \rightarrow 2^n$$

| = <b>2</b> e+m |

|----------------|

|                |

| No | Eingang X <sub>n</sub>  | Momentaner<br>Zustand <b>Z</b> <sub>n</sub> | Folgezustand <b>Z</b> <sub>n+1</sub>   | Ausgang <i>Y<sub>n</sub></i> |  |

|----|-------------------------|---------------------------------------------|----------------------------------------|------------------------------|--|

| 1  | $x_1, x_2, \cdots, x_e$ | $Z_{1n}, Z_{2n}, \cdots, Z_{mn}$            | $z_{1n+1}, z_{2n+1}, \cdots, z_{mn+1}$ | $y_1, y_2, \cdots, y_b$      |  |

| ÷  |                         |                                             |                                        |                              |  |

| ν  |                         |                                             |                                        |                              |  |

e+2m+b

#### Zustandsdiagramm – Mealy

#### Zustandsdiagramm – Moore

Zustände Eingänge Kanten Ausgänge  $e_2$ Knoten Knoten e Zustand j Ausgang h Keine Zustandsänderung (Eigenschleife) Die Eingänge e bewirken die Zustandsänderung aber haben keinen Einfluss auf den Ausgang

#### Automatensynthese

- Zustandsmenge bestimmen

- Ein- und Ausgangvariablen bestimmen und Zustände kodieren

- Zustandsdiagramm zeichnen

- Zustandsfolgetabelle aufstellen

- Die Ausgangs- und Zustandsübertragungsfunktionen herausfinden

- Schaltplan zeichnen

#### Mealy - Moore - Umwandlung

- Mealy lässt sich immer in Moore umwandeln

- Einfach wenn die Zustände immer den gleichen Ausgang produzieren

- Sonst neue Zustände definieren

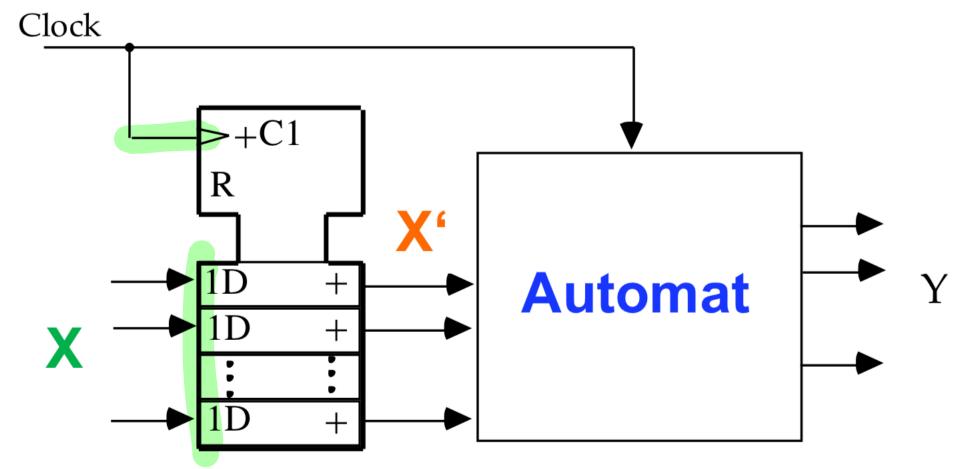

## Dynamisches Verhalten

#### **Mealy-Automat**

• Änderung des Eingangs wird sofort am Ausgang sichtbar

#### **Moore-Automat**

• Änderung des Eingangs wird erst bei der nächsten Taktflanke am Ausgang sichtbar

## Synchronisierung der Eingänge

Eingänge werden gespeichert und erst mit der nächsten Aktiven Taktflanke eingegeben

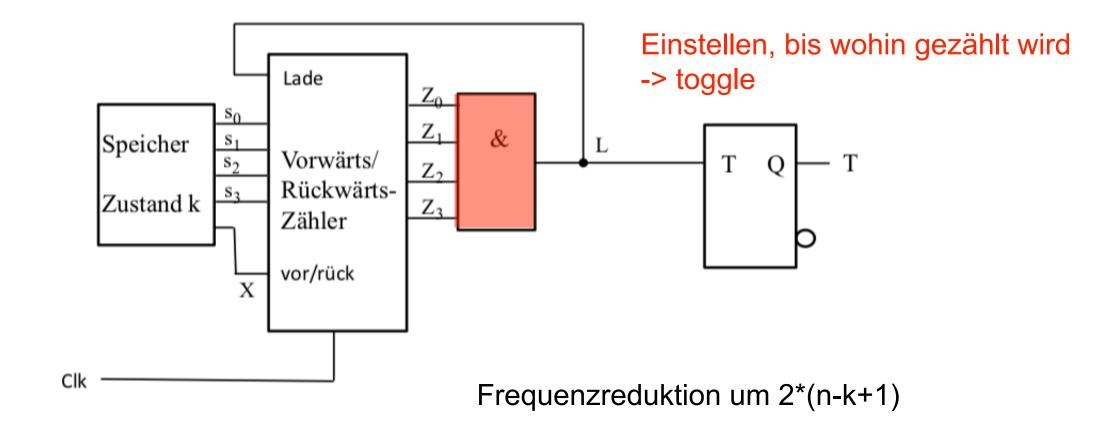

#### Frequenzteiler

Zum reduzieren von Frequenzen

#### Flipflops als Frequenzteiler

• n Flipflops führen zu einer Reduktion von 2^n

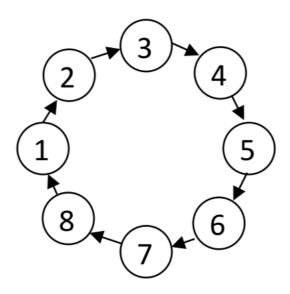

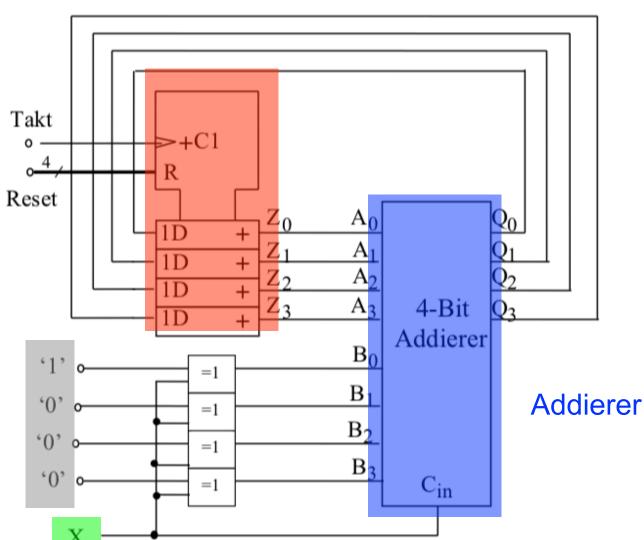

#### Zähler

- Zählen bis zu einer bestimmten Zahl und fangen dann wieder von vorne an

- Vorwärts zählen = +1 in jedem Schritt

- Rückwärts zählen = -1 in jedem Schritt

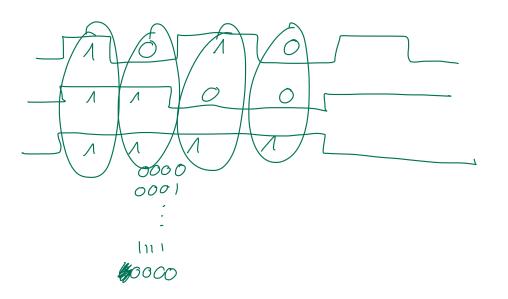

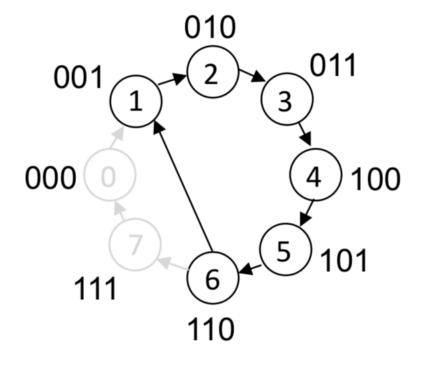

#### Dualzähler = Asynchronzähler

- Kaskadierung von T-Flipflops

- Mit n Flipflops kann man bis 2<sup>n</sup>-1 zählen

- Einzelverzögerungen der Flipflops kumulieren sich → Asynchron

- Maximale Taktfrequenz:  $f_{max} = \frac{1}{\sum_{i=1}^{n} t_{pd_i}}$

#### Modulo-n Zähler

- Zählt bis n und springt dann zurück auf einen vorgegebenen Startzustand

- Umsetzbar als Asynchronzähler und Synchronzähler

#### Modulo-n Asynchronzähler

- Bsp.: Zähler von 1 bis 6

- Umsetzung mit Dualzähler

#### Modulo-n Synchronzähler

- Alle Eingänge liegen auf dem gleichen CLK (schalten gleichzeitig)

- Sind Medwedjew-Automaten

- Entwerfen wie Automaten

Zustandsgraph → Folgezustandstabelle → Karnaugh Diagramme → Schaltplan

## Karnaugh Diagramm & Flipflops

#### D - Flipflops

Karnaughdiagramm normal

#### JK - Flipflops

Karnaughdiagramm mit Felder für Q und !Q

| $Q_3Q_2$ $Q_1$ | 00 | 01 | 11 | 10 |

|----------------|----|----|----|----|

| 0              |    |    |    |    |

| 1              |    |    |    |    |

| $Q_3Q_2$ $Q_1$ | 00 | 01 | 11 | 10 |

|----------------|----|----|----|----|

| 0              |    |    |    |    |

| 1              |    |    |    |    |

$Q_{2n+1}$

#### Reversible Zähler

- Zum vorwärts und rückwärts Zählen

- X = 0: Addition

- X = 1: Subtraktion

4 D-Flipflops mit gleichem CLK

1 wird addiert (subtrahiert)

#### Frequenzteiler mit Zähler

• Um Frequenz beliebig einzustellen

# Speicher

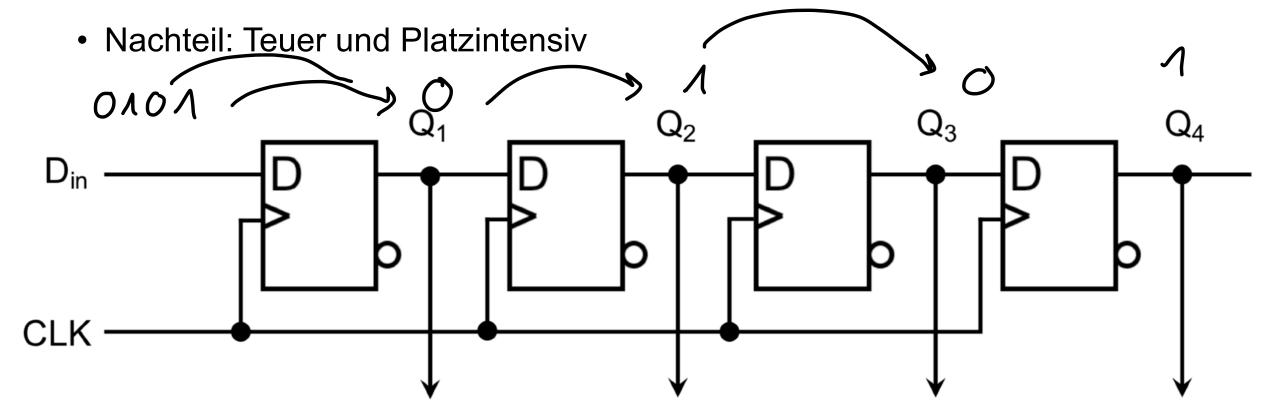

#### Schieberegister

- n = Anzahl Flipflops

- n Bits können gespeichert werden

- n Taktflanken um Bits einzulesen

# Speichermedien

- Magnetband

- Plattenlaufwerk

- DRAM

- Flash

# Speicherfunktionen

- ROM = Read Only Memory

- RAM = Random Access Memory

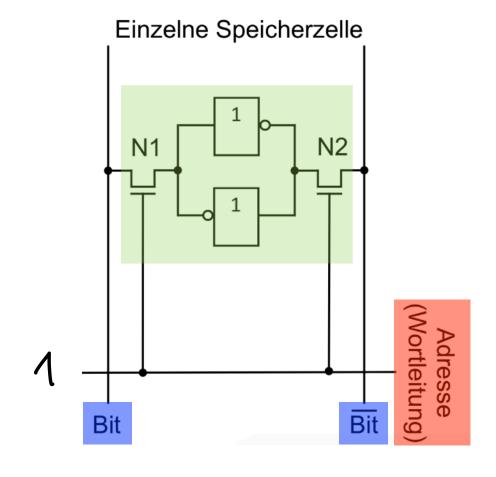

# **SRAM**

- static random access memory

- Speicherzelle wird angewählt

- Speicherinhalt wird gesetzt/gelesen

- lesen: Bit = 1, !Bit = 1

- 1 schreiben: Bit = 1, !Bit = 0

- 0 schreiben: Bit = 0, !Bit = 1

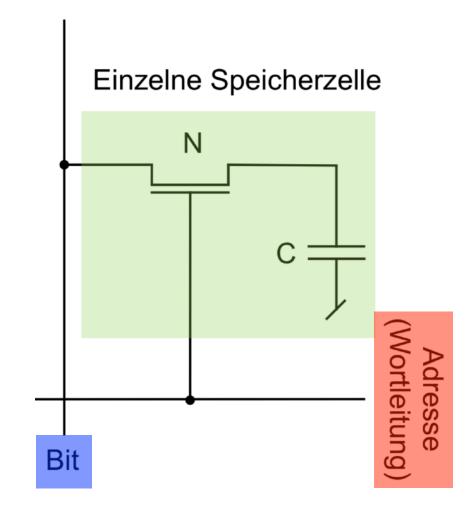

# **DRAM**

- dynamic random access memory

- Speicherzelle wird angewählt

- Speicherinhalt wird gesetzt/gelesen

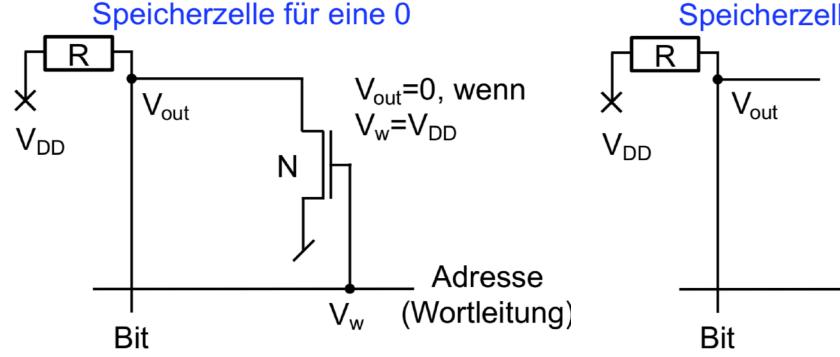

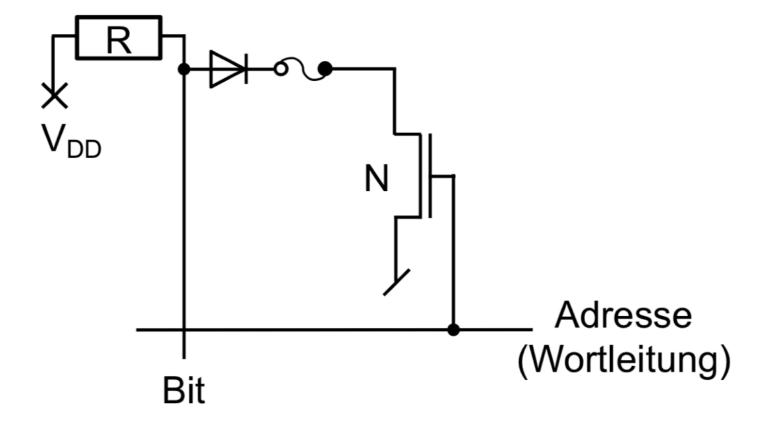

# **ROM**

- Read only memory

- werden bei Produktion programmiert

# Speicherzelle für eine 1 Vout Vout Vout Vout Vout Adresse Vw (Wortleitung)

# **PROM**

- Programmierbare ROM

- Als 1 oder 0 programmierbar

# Basisprüfung

#### Aufgabe A

#### Automaten (30 Punkte)

Die Aufgabe besteht aus **zwei unabhängigen** Teilaufgaben. In Teilaufgabe 1 geht es um das Erstellen des Zustandsgraphen eines Automaten, und in Teilaufgabe 2 soll das Verhalten eines durch ein Zustandsdiagramm beschriebenen Automaten analysiert werden.

#### Teilaufgabe 1: Entwurf eines Automaten

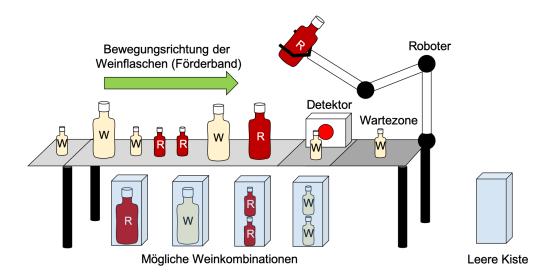

Abbildung A1: Anlage, um Weinflaschen in Kisten zu sortieren un zu packen.

Ein Winzer hat eine neue Anlage bestellt, um die Weinflaschen, die er auf seinem Weinberg produziert, in Kisten zu sortieren und zu packen. In seinem Keller wird Rot- und Weisswein erzeugt. Beide Weinsorten können entweder in kleinen (0.5 Liter) oder in grossen (1 Liter) Flaschen abgefüllt werden. Da alle Kisten die gleiche Grösse haben, werden immer zwei kleine oder eine grosse Flasche(n) zusammengepackt. Rot- und Weisswein werden nie gemischt. Dem Winzer wurde die Anlage in Abbildung A1 vorgeschlagen, der von Ihrer Firma verkauft wird. Als Ingenieur(in) haben Sie jetzt die Aufgabe, einen Automaten zu entwerfen, um diese Anlage zu steuern. Er besteht aus einem Detektor, einem Roboter, einer Wartezone und einer Kontrollstation.

Die Weinflaschen befinden sich zuerst auf einem Förderband und kommen vor dem Detektor vorbei, der die folgenden Signale generiert: **ND**, wenn nichts detektiert wird, **KR** füer kleine Rotwein Flaschen, **KW** füer kleine Weisswein Flaschen, **GR** füer grosse Rotwein Flaschen und **GW** füer grosse Weisswein Flaschen. Wenn der Automat eine grosse Flasche detektiert, schickt er dem Roboter ein **PF** Signal: der Roboter packt diese grosse Flasche in eine Weinkiste. Wenn eine kleine Flasche detektiert wird, prüft zuerst der Automat, ob es schon eine kleine Flasche der gleichen Farbe in der Wartezone gibt:

- wenn ja, dann empfängt der Roboter ein Signal **P2F** und packt die beiden kleinen Flaschen der gleichen Farbe in eine einzige Kiste zusammen. Der Robotor kann die Weinsorten automatisch unterscheiden.

- wenn nicht, dann wird die detektierte kleine Flasche vom Roboter mit dem WZ Befehl in die Wartezone übertragen.

Maximal können sich zwei kleine Weinflaschen von verschiedener Farbe gleichzeitig in der Wartezone befinden. Wenn der Roboter ein MN Signal kriegt, macht er nichts und wartet auf den nächsten Befehl.

#### Aufgaben

- 1. Was sind die Eingänge und die Ausgänge dieses Automaten? Verwenden Sie die folgenden Variablen: GR, GW, KR, KW, MN, ND, PF, P2F und WZ. (2 Punkte)

- 2. Wie viele Bits brauchen Sie, um die Eingangs- und Ausgangsvariablen zu kodieren?  $(1~{\rm Punkt})$

- 3. Zeichnen Sie das Zustandsdiagramm für diese Anlage als **Mealy**-Automat mit der minimalen Anzahl an Zuständen. Definieren Sie N Zustände  $Z_0$  bis  $Z_{N-1}$  und beschreiben Sie deren Funktionalität ganz kurz. Als Eingangs- und Ausgangsvariablen benutzen Sie die Abkürzungen aus Aufgabe 1 (GR, GW, KR,  $\cdots$ ). Hinweis: betrachten Sie den Zustand der Wartezone. (6 Punkte)

- 4. Wie viele Flipflops benötigen Sie minimal, um diesen Automaten zu realisieren? (1 Punkt)

- 5. Wie viele Zeilen und Spalten hätte die komplette Zustandsfolgetabelle? Begründen Sie, (2 Punkte)

- 6. Kann man dieses System auch als  $\mathbf{Moore}$ -Automaten realisieren? Begründen Sie. (1 Punkt)

1. GP, GW, KP, KW, ND = Eingauge 2.

$$3 \rightarrow 2^3 = 8$$

MN, P2F, PF, WZ = Awgauge 2  $\rightarrow 2^2 = 4$

3.  $7 = 8$

GW! PF

GR! PF

ND/MN

Z2: WW

KP(WZ

Z3: PW + WW

ND/MN

RE/P2F

GW! PF

KW/WZ

KP/P2F

KW/WZ

KP/P2F

KW/WZ

KR/WZ

GW! PF

KW/WZ

GR! PF

ND/MN

MMIDM

U. 2FF -> 2<sup>2</sup>=4

S. Zeileu:  $2^{e+m} = 2^{3+2} = 2^{5} = 32$

Spalteu: e + 2m + b = 3 + 2.2 + 2 = 3+4+2 = 9

m= rustandsbits = #FF

6. Ja.

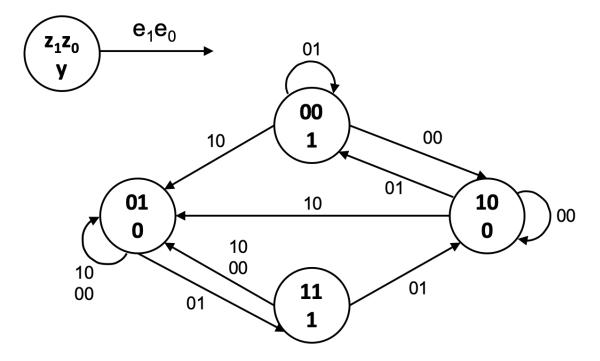

#### Teilaufgabe 2: Analyse des Zustandsdiagramms eines Automaten

Bemerkung: Die Aufgaben in diesem Teil sind unabhängig von den Aufgaben in Teilaufgabe 1.

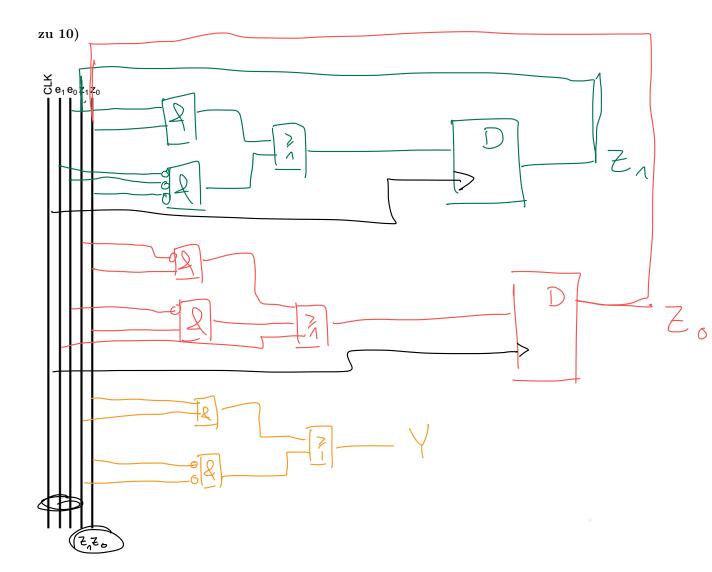

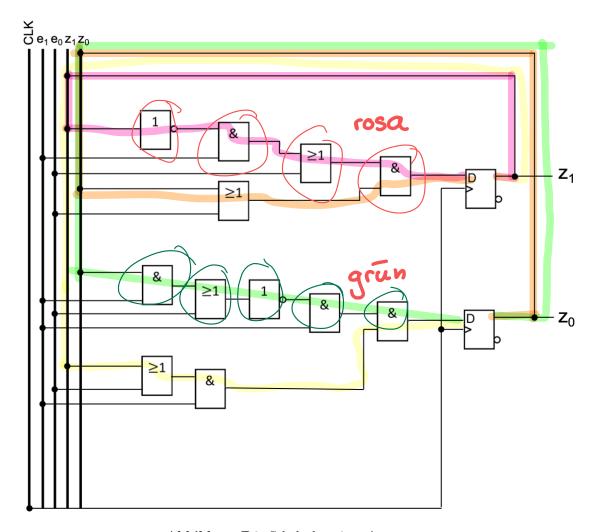

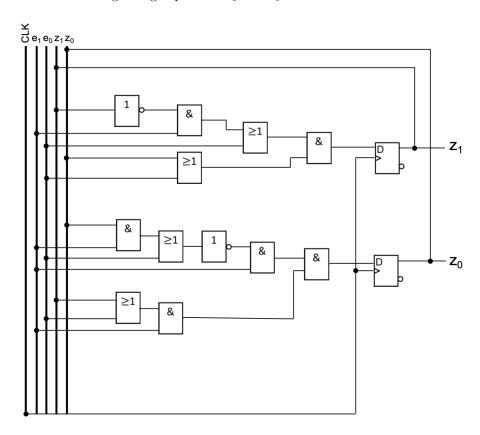

Ein Automat ist durch das Zustandsdiagramm in Abbildung A2 gegeben. Dabei bezeichnet  $\{e_1, e_0\}$  die Eingänge,  $\{y\}$  den Ausgang und  $\{z_1, z_0\}$  die Zustände.

Abbildung A2: Zustandsdiagramm eines Automaten

#### Aufgaben

- 7. Um welchen Automatentyp handelt es sich? Begründen Sie Ihre Antwort. (1 Punkt)

- 8. Ergänzen Sie auf dem Lösungsblatt die Folgezustandstabelle des Automaten. (2 Punkte)

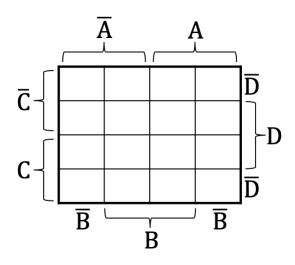

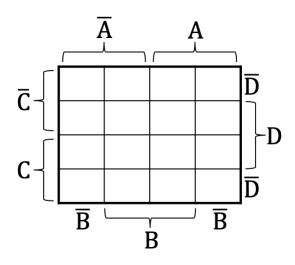

- 9. Erstellen Sie die Karnaugh-Diagramme für die Zustände  $z_{1(n+1)}$  und  $z_{0(n+1)}$  sowie für die Ausgangsvariable  $y_n$  auf dem Lösungsblatt. Geben Sie die minimale disjunktive Normalform (DNF) der Gleichungen für  $z_{1(n+1)}$ ,  $z_{0(n+1)}$  und  $y_n$ . (6 Punkte)

- Zeichnen Sie den Schaltplan dieses Automaten auf dem Lösungsblatt. Ihnen stehen

D-Flipflops sowie NOT, AND und OR Gatter mit einer beliebigen Anzahl an Eingängen

zur Verfügung. (3 Punkte)

Eine  $(e_1,e_0)$  Eingangskombination ist bei diesem Automat unzulässig.

11. Welche ist diese Kombination? (1 Punkt)

12. Wenn diese Eingangskombination trotzdem passiert, sollte der Automat bei der nächsten aktiven Taktflanke in seinem aktuellen Zustand bleiben und in keinen anderen Zustand wechseln. Wie müssen die Gleichungen für  $z_{1(n+1)}$  und  $z_{0(n+1)}$  modifiziert werden, damit diese Bedingung erfüllt wird? Die zusätzlichen Karnaugh-Diagramme auf dem Lösungsblatt können dafür verwendet werden. (4 Punkte)

zu 8)

| e <sub>1</sub> | e <sub>0</sub> | Z <sub>1n</sub> | z <sub>0n</sub> | Z <sub>1n+1</sub> | <b>Z</b> <sub>0n+1</sub> | y <sub>n</sub> |

|----------------|----------------|-----------------|-----------------|-------------------|--------------------------|----------------|

| 0              | 0              | 0               | 0               | N                 | 0                        | 1              |

| 0              | 0              | 0               | 1               | 0                 | Λ                        | 0              |

| 0 .            | 0              | 1               | 0               | Λ                 | 0                        | 0              |

| 0              | 0              | 1               | 1               | 0                 | _/                       | Λ              |

| 0              | 1              | 0               | 0               | 0                 | 0                        | 1              |

| 0              | 1              | 0               | 1               | Λ                 | _/                       | 0              |

| 0              | 1              | 1               | 0               | 0                 | 0                        | 0              |

| 0              | 1              | 1               | 1               | 1                 | 0                        | Λ              |

| 1              | 0              | 0               | 0               | $\bigcirc$        | 1                        | 1              |

| 1              | 0              | 0               | 1               | 0                 | Λ                        | 8              |

| 1              | 0              | 1               | 0               | 0                 | 1                        | 0              |

| 1              | 0              | 1               | 1               | 0                 | V                        | N              |

| 1              | 1              | 0               | 0               | X                 | X                        | 111            |

| 1              | 1              | 0               | 1               | ×                 | X                        | 0/X            |

| 1              | 1              | 1               | 0               | X                 | X                        | 01%            |

| 1              | 1              | 1               | 1               | X                 | X                        | <u>1</u> /X    |

| Z <sub>1n+1</sub> | ı                             | ~          | 2,   | e      | 1          |         |

|-------------------|-------------------------------|------------|------|--------|------------|---------|

|                   | e <sub>1</sub> e <sub>0</sub> | 00         | 01   | 11     | 10         |         |

| -<br>Z, {         | 00                            | 4          | 0    | X      | 0          | -<br>Z0 |

|                   | 01                            |            | 1    | X      | 0          | 7 20    |

| ξ <sub>1</sub> {  | 11                            | $\bigcirc$ | <br> | X      | $\bigcirc$ | 500     |

| " (               | 10                            | 1          | 0    | X      | 0          | 飞。      |

|                   |                               | eo         |      | ,<br>, | e.         |         |

|                   |                                                                | 0          | - 1    | e      | . 1    |

|-------------------|----------------------------------------------------------------|------------|--------|--------|--------|

| z <sub>0n+1</sub> |                                                                | $\sim$     | $\sim$ | $\sim$ | $\sim$ |

|                   | e <sub>1</sub> e <sub>0</sub><br>z <sub>1</sub> z <sub>0</sub> | 00         | 01     | 11     | 10     |

| 5                 | 00                                                             | $\bigcirc$ | 0      | X      | 1      |

| ^ \               | 01                                                             | 1          |        | X      | A      |

| 2, 5              | 11                                                             | <          |        | X      | 1      |

|                   | 10                                                             | $\bigcirc$ | 0      | X      | A      |

|                   |                                                                |            |        | ,      |        |

Zonen = en V ( = 1 1 Zo) V ( eo 1 Zo)

Znnen = (en neo n Zo) V(eo nzo)

| $\mathbf{y}_{n}$ |                   |    |            |    |    |

|------------------|-------------------|----|------------|----|----|

|                  | $e_1e_0$ $z_1z_0$ | 00 | 01         | 11 | 10 |

|                  | 00                |    | /          | X  |    |

|                  | 01                | 0  | 0          | X  | 0  |

|                  | 11                | 1  | 1          | X  |    |

|                  | 10                | 0  | $\bigcirc$ | X  | 0  |

$y = (Z_1 \wedge Z_0) \vee (\overline{Z_1} \wedge \overline{Z_0})$

$$Y = (\overline{Z}_{1} \wedge \overline{Z}_{0}) \vee (\overline{Z}_{1} \wedge \overline{Z}_{0})$$

$$\Lambda\Lambda$$

.  $(\Lambda,\Lambda)$

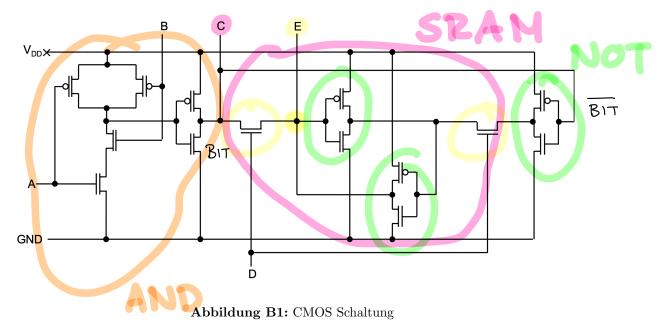

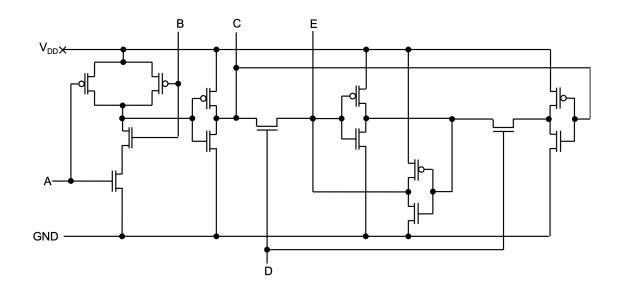

#### Aufgabe B

CMOS (16 Punkte)

In dieser Aufgabe sollen verschiedene Aspekte von CMOS Schaltungen untersucht werden. Hinweis: Die Teilaufgaben 1 und 2 sind voneinander unabhängig.

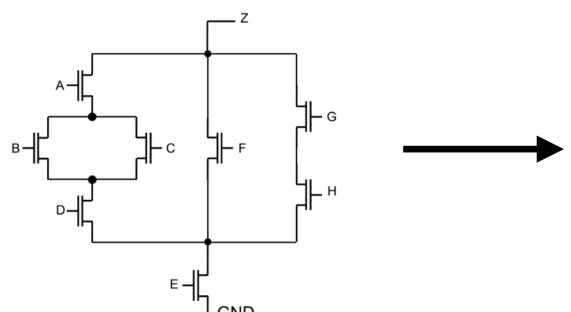

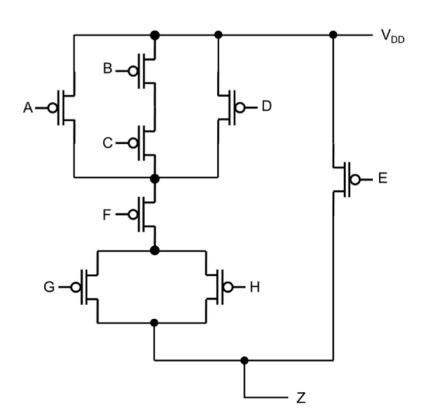

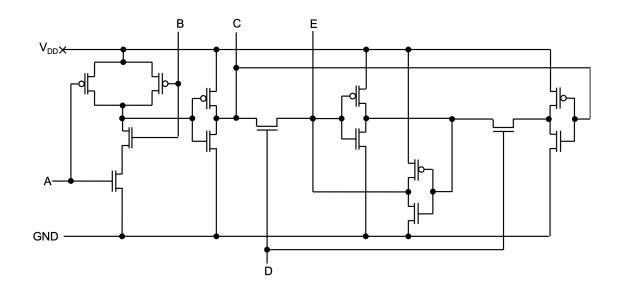

#### Teilaufgabe 1: Analyse einer CMOS Schaltung

In dieser Teilaufgabe soll die gegebene CMOS Schaltung in Abbildung B1 analysiert werden.

- 1. Markieren und bezeichnen Sie die CMOS Blöcke in der Schaltung auf dem Lösungsblatt. Wenn mehrere Blöcke gruppiert werden können, um ein einziges Bauelement zu realisieren, dann muss nur der gesamte Block markiert werden, z.B. NOR+INVERTER→OR

(6 Punkte)

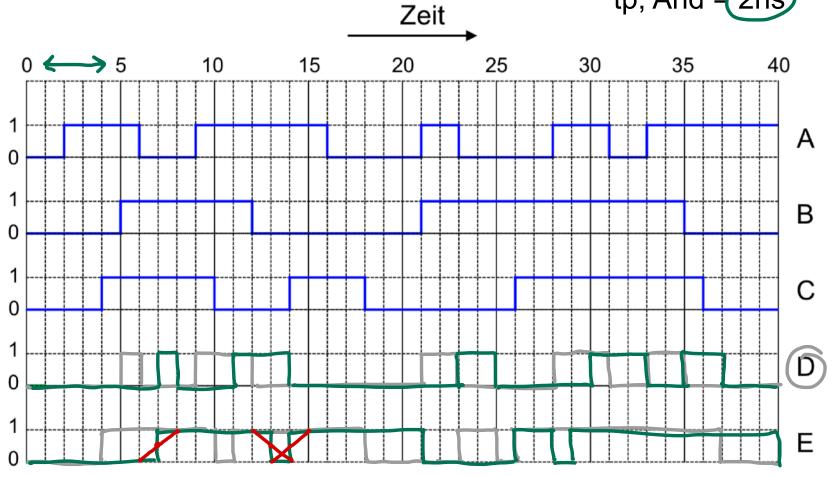

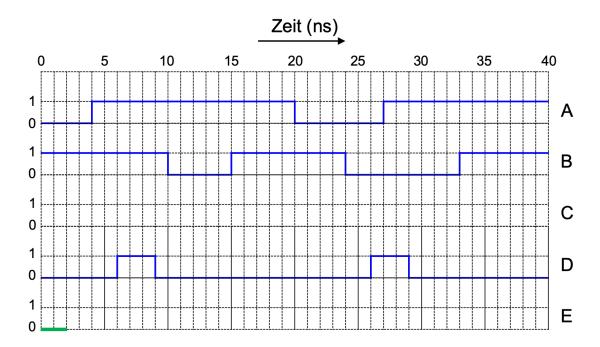

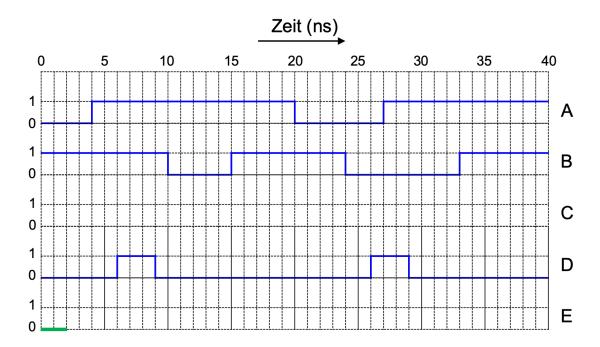

- 2. Vervollständigen Sie das Zeitdiagramm auf dem Lösungsblatt für die Variablen D und E als Funktion von A, B und C. Es wird angenommen, dass die Bauelemente keine Verzögerungszeiten haben. (4 Punkte)

- 2. Zeitdiagramm

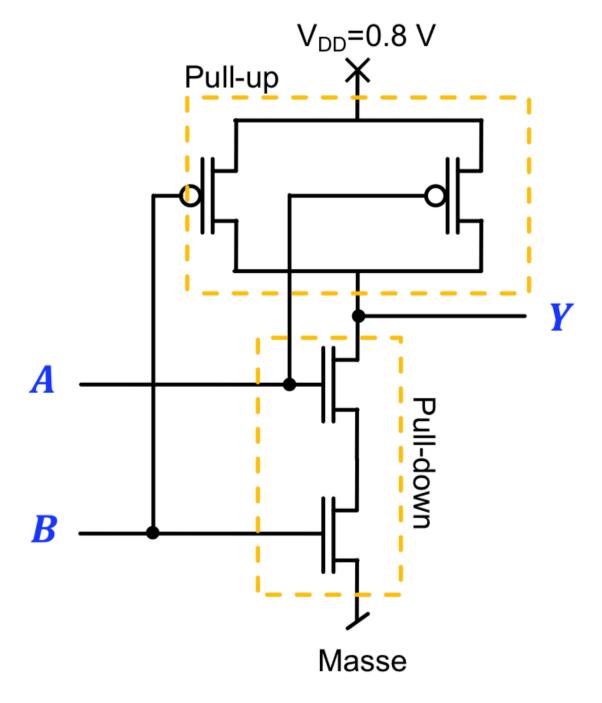

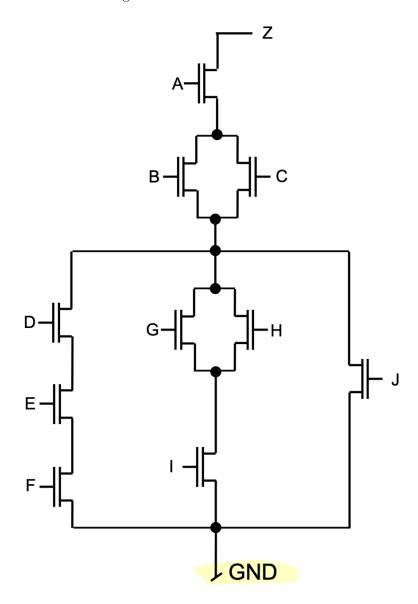

#### Teilaufgabe 2: Pull-up/Pull-down Umwandlung

In dieser Teilaufgabe soll die Schaltung in Abbildung B2 analysiert werden. Damit wird der Pulldown Pfad einer CMOS Schaltung realisiert.

Abbildung B2: Pull-down CMOS Schaltung für die Funktion Z

3. Zeichnen Sie den Pull-up Pfad der Schaltung in Abbildung B2 auf dem Lösungsblatt.

(4 Punkte)

4. Geben Sie die Pull-up und Pull-down Funktionsgleichungen für Z an.

(2 Punkte)

PD: ANCBVC) A ((DAEAF) V J V (IACGUH)))

PO: AV(BAC)V((DVEVF)AJACTV(GAH))) 3. A -0 = D -01= E-01= 3 -0/-C -0 [ ]

#### Aufgabe C

#### Zahlensysteme, Rechnen und Minimieren (20 Punkte)

Die Aufgabe befasst sich im ersten Teil mit der Behandlung von Zahlen aus verschiedenen Zahlensystemen. Achtung: Beachten Sie, dass die Teilaufgaben 1, 2 und 3 unabhängig voneinander zu lösen sind!

#### Teilaufgabe 1: Umrechnung zwischen Zahlensystemen und Dualzahloperationen

- 1. Wandeln Sie −33<sub>10</sub> in eine 8-stellige Zweierkomplementzahl um. (1 Punkt)

- 2. Wandeln Sie die 8-stellige Zweierkomplementzahl 100010002 in die entsprechende ganzzahlige Dezimalzahl um. (1 Punkt)

- 3. Wandeln Sie -7.3<sub>10</sub> so genau wie möglich in eine Zweierkomplementzahl mit 4 Bits vor und 4 Bits nach dem Komma um. Was ist der Absolutbetrag des resultierenden (2 Punkte) Dezimalzahl Fehlers?

- 4. Wandeln Sie die folgende positive Binärzahl 11111001111.1012 in die entsprechende Hexadezimalzahl um. Bitte merken Sie sich, dass es keine Zweierkomplementzahl ist (1 Punkt)

- 5. Zwei positive Binärzahlen A=11100.12 und B=11101.0012 sind gegeben. Gesucht ist C=A-B. Geben Sie A, -B und C als Zweierkomplementzahlen (6 Bits vor dem Komma, 4 (3) Punkte) nach dem Komma) sowie C als Dezimalzahl an.

1.

$$\frac{00100001}{11011110} = 33$$

$$11011111 = -33$$

$$11011111 = -33$$

$$0.3 = (0.0101)_2 = \frac{1}{4} + \frac{1}{16}$$

= 0,3125

$$-2^{7}+2^{3}=-120$$

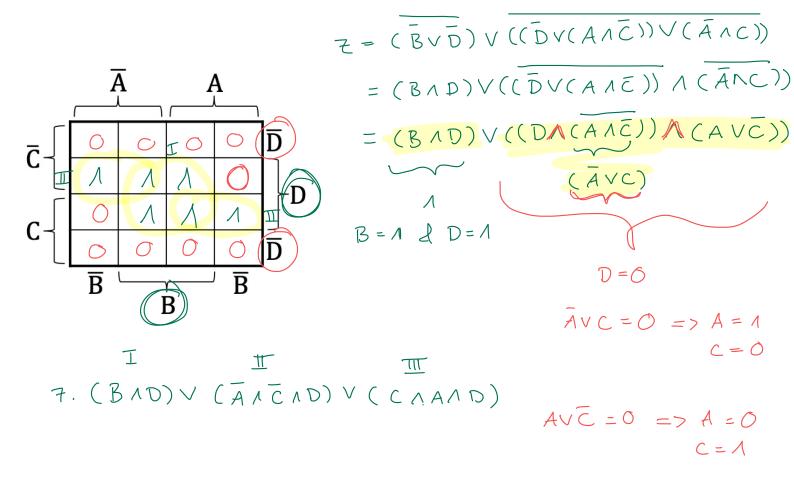

#### Teilaufgabe 2: Logik Minimierung mit Karnaugh-Diagramm

In dieser Aufgabe leiten Sie die minimale disjunktive Normalform (DNF) einer gegebenen Funktion Z mittels Karnaugh-Diagramm her.

Eine kombinatorische Schaltung hat vier Eingänge A, B, C und D und einen Ausgang Z. Der Ausgang ist durch die folgende Funktion beschrieben:

$$Z = \overline{(\overline{B} \vee \overline{D}) \wedge ((\overline{D} \vee (A \wedge \overline{C})) \vee (\overline{A} \wedge C))}$$

#### Aufgaben

- 6. Füllen Sie das Karnaugh-Diagramm für Z auf dem Lösungsblatt aus und identifizieren Sie alle Päckehen, die aus Mintermen bestehen. (4 Punkte)

- 7. Geben Sie die minimale DNF (disjunktive Normalform) von Z als Gleichung an. (2 Punkte)

- 8. Gibt es Hazards? Wenn ja, bei welchem Übergang (welchen Übergängen)? (1 Punkt)

#### Teilaufgabe 3: Logik Minimierung mit Bool'scher Algebra

In dieser Aufgabe müssen zwei Gleichungen anhand der Regel der Bool'schen Algebra minimiert werden.

#### Aufgaben

9. Vereinfachen Sie die folgende logische Gleichung

(2 Punkte)

$$\overline{(A \wedge \overline{B}) \vee (\overline{A} \wedge B)} \wedge (A \vee B)$$

10. Vereinfachen Sie die folgende logische Gleichung

(3 Punkte)

$$((A \wedge \overline{B} \wedge (C \vee (B \wedge D))) \vee \overline{A} \vee B) \wedge \overline{C}$$

9.

$$(A\overline{A}B)V(\overline{A}AB)\Lambda(AVB) = (\overline{A}\overline{A}B)\Lambda(\overline{A}\overline{A}B)\Lambda(AVB)$$

$$=(\overline{A}VB)\Lambda(AVO) = (\overline{A}VB)\Lambda A = \underline{A}\Lambda B$$

# 10. ((AABA(CV(BAD))VĀVB)AC

Institut für Integrierte Systeme

$= \overline{C} \Lambda (\overline{A} \Lambda (\overline{B} \overline{V} \overline{A} \overline{V} C)$

27.01.20

## Aufgabe D

#### Sequenzielle Schaltungen (20 Punkte)

Die Aufgabe besteht aus drei unabhängigen Teilaufgaben.

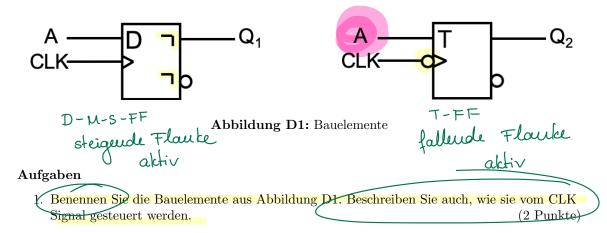

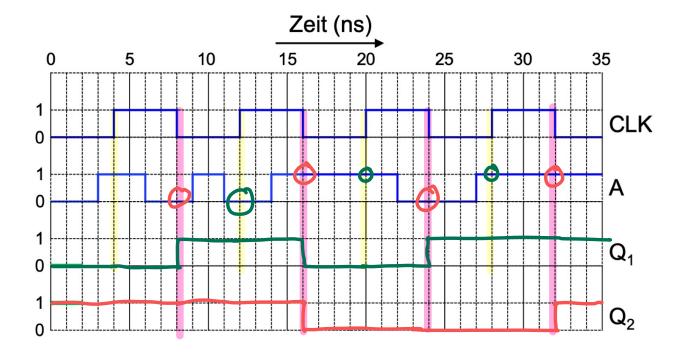

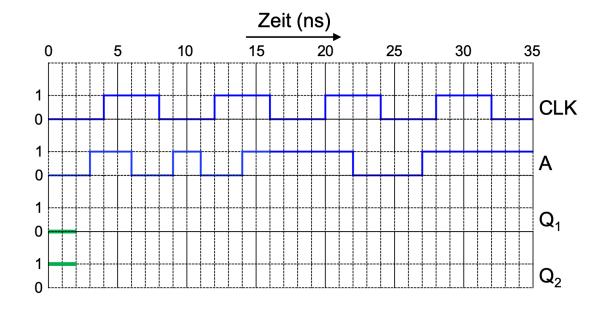

#### Teilaufgabe 1: Latches und Flipflops

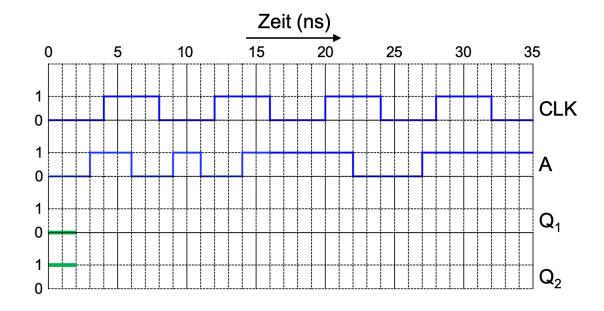

2. Vervollständigen Sie das Zeitdiagramm auf dem Lösungsblatt für die Bauelemente aus Abbildung D1. Es wird angenommen, dass diese Bauelemente keine Verzögerungszeiten haben. (4 Punkte)

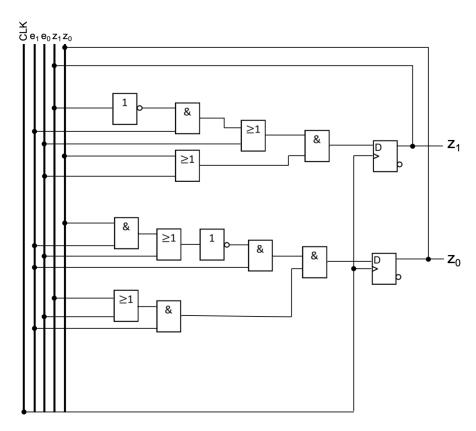

Abbildung D2: Schaltplan eines Automaten

#### Teilaufgabe 2: Taktfrequenzen von Schaltungen

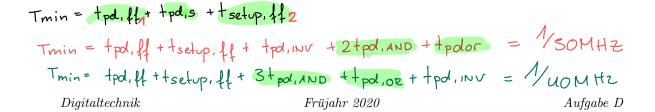

Die folgende Aufgabe bezieht sich auf die Automatenschaltung aus Abbildung D2. Es wurde festgesstellt, dass der Ausgang  $z_1$  mit einer maximalen Taktfrequenz von 50 MHz betrieben werden kann, der Ausgang  $z_0$  mit maximal 40 MHz. Die Durchlaufzeiten aller Bauelemente sowie die Setup- und Hold-Zeiten der Flipflops sind der Tabelle D1 zu entnehmen, ausser die des UND- und ODER-Gatters, die unbekannt sind. Nehmen Sie an, dass alle Signalpegel der Eingänge  $e_1$  und  $e_0$  rechtzeitig stabil anlagen, als die maximalen Taktfrequenzen von  $z_1$  und  $z_0$  gemessen wurde.

#### Aufgaben

- 3. Zeichnen Sie auf dem Lösungsblatt den längsten Signalpfad für  $z_1$  und  $z_0$ . (2 Punkte)

- 4. Geben Sie für diese beiden Signalpfade die Gleichung (Bedingung) an, die die entsprechende minimale Taktperiode bestimmt. Verwenden Sie dafür die Variablennamen aus Tabelle D1. (2 Punkte)

- 5. Aus der gemessenen maximalen Taktfrequenz von  $z_1$  und  $z_0$  können die Durchlaufzeiten  $t_{d,or}$  und  $t_{d,and}$  des ODER und UND Gatters gerechnet werden. Wie gross sind sie?

(3 Punkte)

| D-Flipflop Setup-Zeit    | $t_{setup,dff}$ | 2 ns  |

|--------------------------|-----------------|-------|

| D-Flipflop Durchlaufzeit | $t_{pd,dff}$    | 4 ns  |

| D-Flipflop Hold-Zeit     | $t_{hold,dff}$  | 2 ns  |

| NOT Durchlaufzeit        | $t_{d,not}$     | 1 ns  |

| AND Durchlaufzeit        | $t_{d,and}$     | ?? ns |

| OR Durchlaufzeit         | $t_{d,or}$      | ?? ns |

Tabelle D1: Zeitparameter

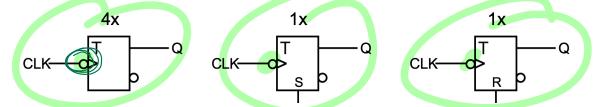

**Abbildung D3:** (links) Normale T-Flipflops. (mitte) T-Flipflop mit einem asynchronen Setz (S) Eingang. (rechts) T-Flipflop mit einem asynchronen Rücksetz (R) Eingang.

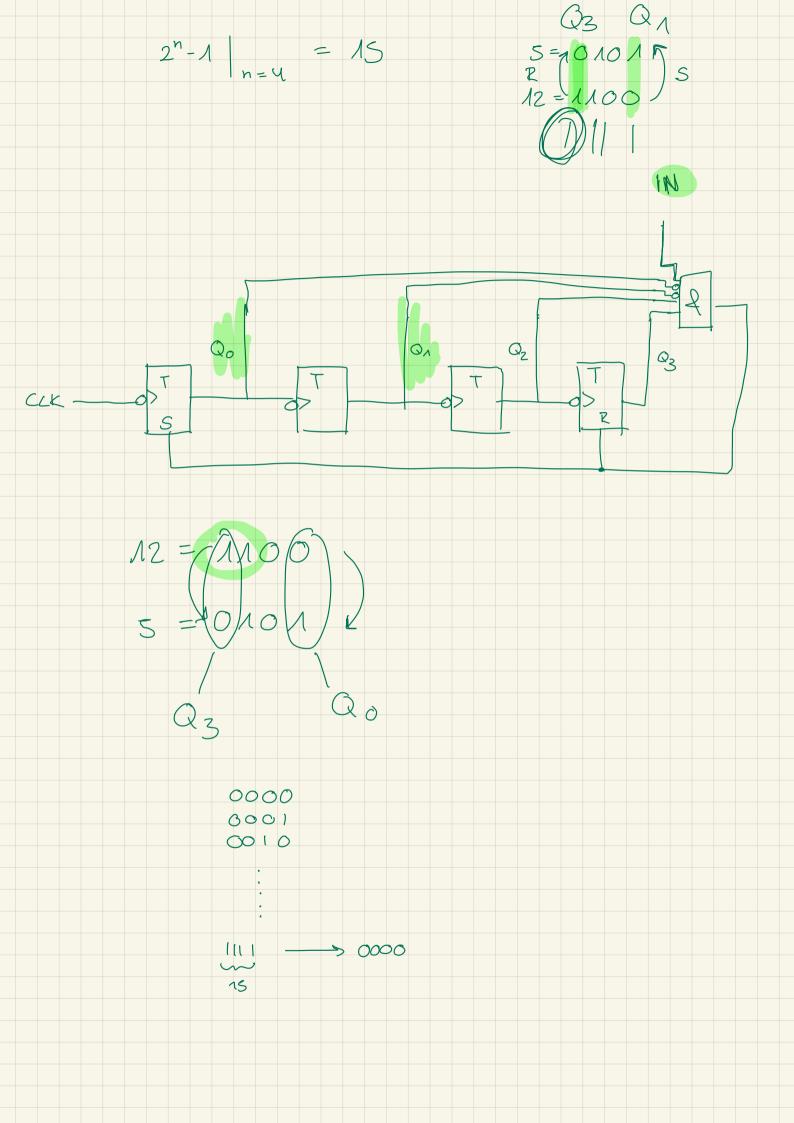

#### Teilaufgabe 3: Asynchronzähler mit T-Flipflops

Das Ziel dieser Teilaufgabe ist, einen asynchronen Binärzähler zu entwerfen, der in der Regel von 0 bis 15 zählt ausser wenn ein Eingangssignal IN=1 ist. In diesem Fall muss er bei 5 neu starten, sobald er 12 erreicht. Alle Zahlen sind als Dualzahlen kodiert. Ihnen stehen 1 T-Flipflop mit einem asynchronen Setz (S) Eingang, 1 T-Flipflop mit einem asynchronen Rücksetz (R) Eingang sowie 4 normale T-Flipflops ohne zusätzliche asynchrone Eingänge zur Verfügung. Diese Bauelemente sind in Abbildung D3 gezeigt.

Beim T-Flipflop mit dem asynchronen Setz Eingang wird der Ausgang Q sofort 1 wenn S=1, unabhängig vom Taktsignal. Beim T-Flipflop mit dem asynchronen Rücksetz Eingang wird der Ausgang Q sofort 0 wenn R=1, auch unabhängig vom Taktsignal. Wenn der zu entwerfende Zähler 12 erreicht und  $\mathbf{IN}=1$ , dann muss er sofort bei 5 neu anfangen. Sonst  $(\mathbf{IN}=0)$  zählt er von 0 bis 15 und fängt dann wieder bei 0 an.

Wenn Sie N Flipflops benötigen, um diesen Zähler aufzubauen, dann sollten die Flipflop Ausgänge benannt werden, wobei  $Q_0$  dem 'least significant bit' entspricht und  $Q_{N-1}$  dem 'most significant bit'.

- 6. Wie viele T Flipflops sind nötig, um diesen Zähler zu realisieren? (1 Punkt)

- 7. Wie viele nicht verwendete Zustände ergeben sich daraus? Begründen Sie Ihre Aussage.

- 8. Was ist die logische Bedingung, damit der Zähler in einen anderen Zustand wechselt, wenn er 12 erreicht? Drücken Sie diese Bedingung als Funktion von den Q-Ausgängen und vom IN Signal aus. (1 Punkt)

- 9. Zeichnen Sie diesen Zähler auf dem Lösungsblatt. Benützen Sie die T-Flipflops aus Abbildung D3 sowie NICHT, UND und ODER Gatter mit einer beliebigen Anzahl an Eingängen. (4 Punkte)

8.

$$12 = 1100 \quad \text{IN} \land \overline{Q_0} \land \overline{Q_1} \land Q_2 \land Q_3 = 1$$

| T / 1 |      |      |      |  |

|-------|------|------|------|--|

| Kode: | <br> | <br> | <br> |  |

# Basisprüfung D-ITET

#### Digitaltechnik

27. Januar 2020

Hinweise zu den Aufgaben:

• Punktezahl pro Aufgabe:

| Ritte | leer                        | lassen! |

|-------|-----------------------------|---------|

| Duuce | $\iota\iota\iota\iota\iota$ | iussen. |

|        |    | Punkte | Visum |

|--------|----|--------|-------|

| A:     | 30 |        |       |

| B:     | 16 |        |       |

| C:     | 20 |        |       |

| D:     | 20 |        |       |

| Total: | 86 |        |       |

- Schreiben Sie auf jedes Blatt Ihren Kode, der Ihnen auf dem Deckblatt zugeteilt worden ist.

- Beantworten Sie nur gestellte Fragen.

- Sollten Unklarheiten auftreten, wenden Sie sich an die Betreuer.

- Die Aufgaben können in beliebiger Reihenfolge gelöst werden.

- Resultate können nur bewertet werden, wenn ihre Herleitung bzw. Begründung in der angegebenen Lösung enthalten ist.

- Folgefehler werden berücksichtigt.

- Benutzen Sie für die Lösungen ausschliesslich die vorgedruckten Lösungsblätter. Sie können jederzeit neue Blätter bei einem Betreuer verlangen. Beachten Sie, dass auf jedem Lösungsblatt steht, für welche Aufgabe es gedacht ist.

- Benutzen Sie einen dokumentenechten Schreiber, d.h. Kugelschreiber, Füllfederhalter o.ä. Bitte fertigen Sie die Prüfung nicht mit Bleistift an, keine rote Farbe!

- Es sind keine Kommunikationsmittel und keine Rechner erlaubt.

- Beschriebene Blätter sind verdeckt abzulegen.

- $\bullet\,$  Nach Prüfungsende können keine weiteren Blätter abgegeben werden.

- Legen Sie bitte Ihre Legi auf den Tisch. Es wird eine Kontrolle durchgeführt.

$Digital technik \hspace{2cm} 27.01.2020$

# Aufgabe A

Automaten (30 Punkte)

Kode: .....

#### Teilaufgabe 1: Entwurf eines Automaten

1. Eingänge:

Ausgänge:

2. Anzahl an Kodierungsbits für die Eingänge:

Anzahl an Kodierungsbits für die Ausgänge:

3. Zustandsdiagramm für die zu entwerfen Anlage als **Mealy**-Automat und Beschreibung der Zustände:

| Lösungsblatt zu | Kode: |

|-----------------|-------|

| Aufgabe A       |       |

- 4. Minimale Anzahl an Flipflops für die Realisierung dieses Automaten:

- 5. Anzahl an Zeilen der kompletten Zustandsfolgetabelle:

$\label{lem:anzahl} Anzahl \ an \ Spalten \ der \ kompletten \ Zustandsfolgetabelle:$

Begründung:

6. Kann dieser Automat auch als Moore-Automat realisiert werden (mit Begründung)?:

#### Teilaufgabe 2: Analyse des Zustandsdiagramms eines Automaten

7. Automatentyp und Begründung:

zu 8)

| e <sub>1</sub> | e <sub>o</sub> | Z <sub>1n</sub> | Z <sub>0n</sub> | <b>Z</b> <sub>1n+1</sub> | <b>Z</b> <sub>0n+1</sub> | <b>y</b> <sub>n</sub> |

|----------------|----------------|-----------------|-----------------|--------------------------|--------------------------|-----------------------|

| 0              | 0              | 0               | 0               |                          |                          |                       |

| 0              | 0              | 0               | 1               |                          |                          |                       |

| 0              | 0              | 1               | 0               |                          |                          |                       |

| 0              | 0              | 1               | 1               |                          |                          |                       |

| 0              | 1              | 0               | 0               |                          |                          |                       |

| 0              | 1              | 0               | 1               |                          |                          |                       |

| 0              | 1              | 1               | 0               |                          |                          |                       |

| 0              | 1              | 1               | 1               |                          |                          |                       |

| 1              | 0              | 0               | 0               |                          |                          |                       |

| 1              | 0              | 0               | 1               |                          |                          |                       |

| 1              | 0              | 1               | 0               |                          |                          |                       |

| 1              | 0              | 1               | 1               |                          |                          |                       |

| 1              | 1              | 0               | 0               |                          |                          |                       |

| 1              | 1              | 0               | 1               |                          |                          |                       |

| 1              | 1              | 1               | 0               |                          |                          |                       |

| 1              | 1              | 1               | 1               |                          |                          |                       |

### Aufgabe A

zu 9)

z<sub>1n+1</sub>

| $e_1e_2$ | 00 | 01 | 11 | 10 |

|----------|----|----|----|----|

| 00       |    |    |    |    |

| 01       |    |    |    |    |

| 11       |    |    |    |    |

| 10       |    |    |    |    |

**Z**<sub>0n+1</sub>

| $e_1e_0$ | 00 | 01 | 11 | 10 |

|----------|----|----|----|----|

| 00       |    |    |    |    |

| 01       |    |    |    |    |

| 11       |    |    |    |    |

| 10       |    |    |    |    |

$\mathbf{y}_{\mathsf{n}}$

| $e_1e_0$ $z_1z_0$ | 00 | 01 | 11 | 10 |

|-------------------|----|----|----|----|

| 00                |    |    |    |    |

| 01                |    |    |    |    |

| 11                |    |    |    |    |

| 10                |    |    |    |    |

$$z_{1(n+1)} =$$

$$z_{0(n+1)} =$$

$$y_n =$$

11. Unzulässige Eingangskombination:

zu 12)

Z<sub>1n+1</sub>

| e <sub>1</sub> e <sub>0</sub><br>z <sub>1</sub> z <sub>0</sub> | 00 | 01 | 11 | 10 |

|----------------------------------------------------------------|----|----|----|----|

| 00                                                             |    |    |    |    |

| 01                                                             |    |    |    |    |

| 11                                                             |    |    |    |    |

| 10                                                             |    |    |    |    |

**Z**<sub>0n+1</sub>

| e <sub>1</sub> e <sub>0</sub><br>z <sub>1</sub> z <sub>0</sub> | 00 | 01 | 11 | 10 |

|----------------------------------------------------------------|----|----|----|----|

| 00                                                             |    |    |    |    |

| 01                                                             |    |    |    |    |

| 11                                                             |    |    |    |    |

| 10                                                             |    |    |    |    |

$z_{1(n+1)} =$

$z_{0(n+1)} =$

Erreichte Punkte:

| 1)       | /2  |

|----------|-----|

| 2)<br>3) | /1  |

| 3)       | /6  |

| 4)       | /1  |

| 4)<br>5) | /2  |

| 6)       | /1  |

| 7)<br>8) | /1  |

| 8)       | /2  |

| 9)       | /6  |

| 10)      | /3  |

| 11)      | /1  |

| 12)      | /4  |

| Total    | /30 |

|          |     |

# Aufgabe B

CMOS (16 Punkte)

#### Teilaufgabe 1: Analyse einer CMOS Schaltung

1. Kennzeichnen der CMOS Blöcke:

#### 2. Zeitdiagramm

Aufgabe B

#### Teilaufgabe 2: Pull-up/Pull-down Umwandlung

3. Pull-up Pfad:

#### 4. Funktionsgleichungen:

$$Z_{Pull-up} =$$

$$Z_{Pull-down} =$$

#### Erreichte Punkte:

| Effeichte Funkte. |     |

|-------------------|-----|

| 1)                | /6  |

| 2)                | /4  |

| 3)                | /4  |

| 4)                | /2  |

| Total             | /16 |

C als Zweierkomplementzahl:

C als Dezimalzahl:

Teilaufgabe 2: Logik Minimierung mit Karnaugh-Diagramm zu 6)

7. Z =

8. Hazards?

Bei welchem Übergang (welchen Übergängen)?

Teilaufgabe 3: Logik Minimierung mit Bool'scher Algebra

9.

$$\overline{(A \wedge \overline{B}) \vee (\overline{A} \wedge B)} \wedge (A \vee B) =$$

10.

$$((A \wedge \overline{B} \wedge (C \vee (B \wedge D))) \vee \overline{A} \vee B) \wedge \overline{C} =$$

#### Erreichte Punkte:

| 1)       | /1  |

|----------|-----|

| 2)<br>3) | /1  |

|          | /2  |

| 4)       | /1  |

| 5)       | /3  |

| 6)       | /4  |

| 7)       | /2  |

| 8)       | /1  |

| 9)       | /2  |

| 10)      | /3  |

| Total    | /20 |

Aufgabe D

### Aufgabe D

Sequenzielle Schaltungen (20 Punkte)

#### Teilaufgabe 1: Latches und Flipflops

1. Benennung der Bauteile

Links:

Rechts:

2. Zeitdiagramm für die Bauelemente aus Abbildung D1:

#### Teilaufgabe 2: Taktfrequenzen von Schaltungen

3. Zeichnen Sie das längste Signalpfad für  $z_1$  und  $z_0$ .

4. Gleichung (Bedingung) für die minimale Taktperiode, die jedem Signalpfad entspricht

$$T_{min,z_1} \ge$$

$$T_{min,z_0} \ge$$

5.

$$t_{d,and}$$

=

$$t_{d,or} =$$

| Lösungsblatt zu                                              | Kode:                       |

|--------------------------------------------------------------|-----------------------------|

| Aufgabe D                                                    |                             |

|                                                              |                             |

| Teilaufgabe 3: Asynchronzähler mit T-Flipflops               |                             |

| 6. Anzahl an T-Flipflops:                                    |                             |

|                                                              |                             |

|                                                              |                             |

|                                                              |                             |

| 7. Anzahl nicht verwendeter Zustände:                        |                             |

|                                                              |                             |

|                                                              |                             |

|                                                              |                             |

| 8. Bedingung, damit der Zähler in einen anderen Zustand wech | nselt, wenn er 12 erreicht: |

|                                                              |                             |

|                                                              |                             |

9. Zähler Schaltung mit T-Flipflops:

#### Erreichte Punkte:

| 1110101        | ico i aimico. |

|----------------|---------------|

| 1)             | /2            |

| 1)<br>2)<br>3) | /4            |

|                | /2            |

| 4)             | /2            |

| 5)             | /3            |

| 6)             | /1            |

| 7)             | /1            |

| 8)             | /1            |

| 9)             | /4            |

| Total          | /20           |

| T / 1 |      |      |      |  |

|-------|------|------|------|--|

| Kode: | <br> | <br> | <br> |  |

# Basisprüfung D-ITET

#### Digitaltechnik

27. Januar 2020

Hinweise zu den Aufgaben:

• Punktezahl pro Aufgabe:

| Ritte | leer                        | lassen! |

|-------|-----------------------------|---------|

| Duuce | $\iota\iota\iota\iota\iota$ | iussen. |

|        |    | Punkte | Visum |

|--------|----|--------|-------|

| A:     | 30 |        |       |

| B:     | 16 |        |       |

| C:     | 20 |        |       |

| D:     | 20 |        |       |

| Total: | 86 |        |       |

- Schreiben Sie auf jedes Blatt Ihren Kode, der Ihnen auf dem Deckblatt zugeteilt worden ist.

- Beantworten Sie nur gestellte Fragen.

- Sollten Unklarheiten auftreten, wenden Sie sich an die Betreuer.

- Die Aufgaben können in beliebiger Reihenfolge gelöst werden.

- Resultate können nur bewertet werden, wenn ihre Herleitung bzw. Begründung in der angegebenen Lösung enthalten ist.

- Folgefehler werden berücksichtigt.

- Benutzen Sie für die Lösungen ausschliesslich die vorgedruckten Lösungsblätter. Sie können jederzeit neue Blätter bei einem Betreuer verlangen. Beachten Sie, dass auf jedem Lösungsblatt steht, für welche Aufgabe es gedacht ist.

- Benutzen Sie einen dokumentenechten Schreiber, d.h. Kugelschreiber, Füllfederhalter o.ä. Bitte fertigen Sie die Prüfung nicht mit Bleistift an, keine rote Farbe!

- Es sind keine Kommunikationsmittel und keine Rechner erlaubt.

- Beschriebene Blätter sind verdeckt abzulegen.

- $\bullet\,$  Nach Prüfungsende können keine weiteren Blätter abgegeben werden.

- Legen Sie bitte Ihre Legi auf den Tisch. Es wird eine Kontrolle durchgeführt.

$Digital technik \hspace{2cm} 27.01.2020$

## Aufgabe A

Automaten (30 Punkte)

Kode: .....

#### Teilaufgabe 1: Entwurf eines Automaten

1. Eingänge:

Ausgänge:

2. Anzahl an Kodierungsbits für die Eingänge:

Anzahl an Kodierungsbits für die Ausgänge:

3. Zustandsdiagramm für die zu entwerfen Anlage als **Mealy**-Automat und Beschreibung der Zustände:

| Lösungsblatt zu | Kode: |

|-----------------|-------|

| Aufgabe A       |       |

- 4. Minimale Anzahl an Flipflops für die Realisierung dieses Automaten:

- 5. Anzahl an Zeilen der kompletten Zustandsfolgetabelle:

$\label{lem:anzahl} Anzahl \ an \ Spalten \ der \ kompletten \ Zustandsfolgetabelle:$

Begründung:

6. Kann dieser Automat auch als Moore-Automat realisiert werden (mit Begründung)?:

#### Teilaufgabe 2: Analyse des Zustandsdiagramms eines Automaten

7. Automatentyp und Begründung:

zu 8)

| e <sub>1</sub> | e <sub>o</sub> | Z <sub>1n</sub> | Z <sub>0n</sub> | <b>Z</b> <sub>1n+1</sub> | <b>Z</b> <sub>0n+1</sub> | <b>y</b> <sub>n</sub> |

|----------------|----------------|-----------------|-----------------|--------------------------|--------------------------|-----------------------|

| 0              | 0              | 0               | 0               |                          |                          |                       |

| 0              | 0              | 0               | 1               |                          |                          |                       |

| 0              | 0              | 1               | 0               |                          |                          |                       |

| 0              | 0              | 1               | 1               |                          |                          |                       |

| 0              | 1              | 0               | 0               |                          |                          |                       |

| 0              | 1              | 0               | 1               |                          |                          |                       |

| 0              | 1              | 1               | 0               |                          |                          |                       |

| 0              | 1              | 1               | 1               |                          |                          |                       |

| 1              | 0              | 0               | 0               |                          |                          |                       |

| 1              | 0              | 0               | 1               |                          |                          |                       |

| 1              | 0              | 1               | 0               |                          |                          |                       |

| 1              | 0              | 1               | 1               |                          |                          |                       |

| 1              | 1              | 0               | 0               |                          |                          |                       |

| 1              | 1              | 0               | 1               |                          |                          |                       |

| 1              | 1              | 1               | 0               |                          |                          |                       |

| 1              | 1              | 1               | 1               |                          |                          |                       |

### Aufgabe A

zu 9)

z<sub>1n+1</sub>

| $e_1e_2$ | 00 | 01 | 11 | 10 |

|----------|----|----|----|----|

| 00       |    |    |    |    |

| 01       |    |    |    |    |

| 11       |    |    |    |    |

| 10       |    |    |    |    |

**Z**<sub>0n+1</sub>

| $e_1e_0$ | 00 | 01 | 11 | 10 |

|----------|----|----|----|----|

| 00       |    |    |    |    |

| 01       |    |    |    |    |

| 11       |    |    |    |    |

| 10       |    |    |    |    |

$\mathbf{y}_{\mathsf{n}}$

| $e_1e_0$ $z_1z_0$ | 00 | 01 | 11 | 10 |

|-------------------|----|----|----|----|

| 00                |    |    |    |    |

| 01                |    |    |    |    |

| 11                |    |    |    |    |

| 10                |    |    |    |    |

$$z_{1(n+1)} =$$

$$z_{0(n+1)} =$$

$$y_n =$$

Aufgabe A

zu 10)

11. Unzulässige Eingangskombination:

zu 12)

Z<sub>1n+1</sub>

| e <sub>1</sub> e <sub>0</sub><br>z <sub>1</sub> z <sub>0</sub> | 00 | 01 | 11 | 10 |

|----------------------------------------------------------------|----|----|----|----|

| 00                                                             |    |    |    |    |

| 01                                                             |    |    |    |    |

| 11                                                             |    |    |    |    |

| 10                                                             |    |    |    |    |

**Z**<sub>0n+1</sub>

| e <sub>1</sub> e <sub>0</sub><br>z <sub>1</sub> z <sub>0</sub> | 00 | 01 | 11 | 10 |

|----------------------------------------------------------------|----|----|----|----|

| 00                                                             |    |    |    |    |

| 01                                                             |    |    |    |    |

| 11                                                             |    |    |    |    |

| 10                                                             |    |    |    |    |

$z_{1(n+1)} =$

$z_{0(n+1)} =$

Erreichte Punkte:

| 1)       | /2  |

|----------|-----|

| 2)<br>3) | /1  |

| 3)       | /6  |

| 4)       | /1  |

| 4)<br>5) | /2  |

| 6)       | /1  |

| 7)<br>8) | /1  |

| 8)       | /2  |

| 9)       | /6  |

| 10)      | /3  |

| 11)      | /1  |

| 12)      | /4  |

| Total    | /30 |

|          |     |

## Aufgabe B

CMOS (16 Punkte)

#### Teilaufgabe 1: Analyse einer CMOS Schaltung

1. Kennzeichnen der CMOS Blöcke:

### 2. Zeitdiagramm

Aufgabe B

#### Teilaufgabe 2: Pull-up/Pull-down Umwandlung

3. Pull-up Pfad:

#### 4. Funktionsgleichungen:

$$Z_{Pull-up} =$$

$$Z_{Pull-down} =$$

#### Erreichte Punkte:

| Effeichte Funkte: |     |  |

|-------------------|-----|--|

| 1)                | /6  |  |

| 2)                | /4  |  |

| 3)                | /4  |  |

| 4)                | /2  |  |

| Total             | /16 |  |

C als Zweierkomplementzahl:

C als Dezimalzahl:

Teilaufgabe 2: Logik Minimierung mit Karnaugh-Diagramm zu 6)

7. Z =

8. Hazards?

Bei welchem Übergang (welchen Übergängen)?

Teilaufgabe 3: Logik Minimierung mit Bool'scher Algebra

9.

$$\overline{(A \wedge \overline{B}) \vee (\overline{A} \wedge B)} \wedge (A \vee B) =$$

10.

$$((A \wedge \overline{B} \wedge (C \vee (B \wedge D))) \vee \overline{A} \vee B) \wedge \overline{C} =$$

#### Erreichte Punkte:

| 1)       | /1  |

|----------|-----|

| 2)<br>3) | /1  |

| 3)       | /2  |

| 4)       | /1  |

| 5)       | /3  |

| 6)       | /4  |

| 7)       | /2  |

| 8)       | /1  |

| 9)       | /2  |

| 10)      | /3  |

| Total    | /20 |

# Aufgabe D

Aufgabe D

Sequenzielle Schaltungen (20 Punkte)

#### Teilaufgabe 1: Latches und Flipflops

1. Benennung der Bauteile

Links:

Rechts:

2. Zeitdiagramm für die Bauelemente aus Abbildung D1:

#### Teilaufgabe 2: Taktfrequenzen von Schaltungen

3. Zeichnen Sie das längste Signalpfad für  $z_1$  und  $z_0$ .

4. Gleichung (Bedingung) für die minimale Taktperiode, die jedem Signalpfad entspricht

$$T_{min,z_1} \ge$$

$$T_{min,z_0} \ge$$

5.

$$t_{d,and}$$

=

$$t_{d,or} =$$

| Lösungsblatt zu                                              | Kode:                       |

|--------------------------------------------------------------|-----------------------------|

| Aufgabe D                                                    |                             |

|                                                              |                             |

| Teilaufgabe 3: Asynchronzähler mit T-Flipflops               |                             |

| 6. Anzahl an T-Flipflops:                                    |                             |

|                                                              |                             |

|                                                              |                             |

|                                                              |                             |

| 7. Anzahl nicht verwendeter Zustände:                        |                             |

|                                                              |                             |

|                                                              |                             |

|                                                              |                             |

| 8. Bedingung, damit der Zähler in einen anderen Zustand wech | nselt, wenn er 12 erreicht: |

|                                                              |                             |

|                                                              |                             |

9. Zähler Schaltung mit T-Flipflops:

| Kode: |  |

|-------|--|

|       |  |

#### Erreichte Punkte:

| Effective I diffice. |     |  |

|----------------------|-----|--|

| 1)                   | /2  |  |

| 2) 3)                | /4  |  |

| 3)                   | /2  |  |

| 4)                   | /2  |  |

| 5)                   | /3  |  |

| 6)                   | /1  |  |

| 7)                   | /1  |  |

| 8)                   | /1  |  |

| 9)                   | /4  |  |

| Total                | /20 |  |

# Tipps

# **Tipps**

- Macht euch klar, was eure Stärken sind.

- Ihr müsst nicht alles lösen.

# Fragen?

# Viel Erfolg!